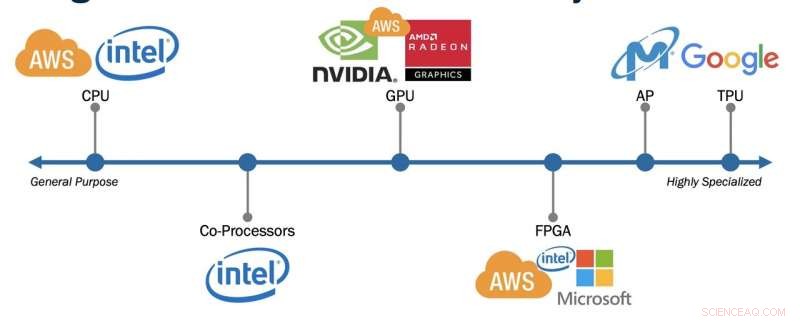

Empresas como Google, Amazonas, e Intel han adoptado ampliamente diferentes tipos de aceleradores de hardware en sus procesos de computación en la nube, pero muchos programas aún no pueden aprovecharlos al máximo. Crédito:Universidad de Michigan

Una nueva técnica desarrollada por investigadores de la Universidad de Michigan podría permitir una adopción más amplia de los componentes informáticos posteriores a la Ley de Moore a través de la traducción automática de códigos. El sistema, llamado AutomataSynth, permite a los ingenieros de software aprovechar el poder de los aceleradores de hardware como los FPGA sin conocimientos de programación especializados o sin necesidad de reescribir los antiguos, Código centrado en CPU.

Con la Ley de Moore llegando a su fin, las empresas y los diseñadores confían en una serie de técnicas de hardware para eludir los rendimientos decrecientes que proporcionan las nuevas CPU. Entre los candidatos a corto plazo más viables se encuentran los aceleradores de hardware como los arreglos de puertas programables en campo (FPGA), que se puede dedicar a ejecutar rápidamente funciones comunes particulares y eliminar cuellos de botella en aplicaciones más grandes.

Si bien su adopción por parte de empresas como Microsoft y Amazon Web Services ya está en marcha, Los FPGA están limitados en su uso por requisitos de programación que son ajenos a muchos desarrolladores de software. Estos requisitos también limitan su uso en software heredado preexistente, que normalmente se escribió para funcionar específicamente con CPU.

La mayoría de los programas que se utilizan hoy en día deben reescribirse por completo a un nivel muy bajo para aprovechar los beneficios de la aceleración de hardware. Debido a esto, los componentes se instalan más rápidamente de lo que realmente se utilizan.

"Las empresas están tomando medidas para tratar de hacer que [las FPGA] sean más accesibles para las personas, "dice Kevin Angstadt, un doctorado candidato que lidera el proyecto, "pero cuando se trata de escribir programas nuevos, el proceso es todavía muy primitivo ".

El equipo, que incluye a los Profs. Westley Weimer y Jean-Baptiste Jeannin, buscó romper esas barreras de adopción reescribiendo automáticamente ciertas funciones de bajo nivel utilizadas por muchas aplicaciones más grandes. Implementado a escala, esto significaría que los desarrolladores podrían hacer un uso completo de los FPGA simplemente agregando algunas líneas a su código existente, sin necesidad de reescribirlo.

Angstadt compara el proceso con la adaptación de las unidades de procesamiento de gráficos (GPU) a la computación de propósito general, inicialmente habilitado por la plataforma CUDA de NVIDIA. CUDA proporcionó a los desarrolladores una interfaz a través de la cual podían aprovechar la potencia de procesamiento de una GPU en tareas no gráficas.

"El objetivo de este trabajo era hacer algo similar con las FPGA, ", Dice Angstadt." No puedes escribir en el mismo idioma cuando los estás usando, pero podemos darte la ilusión de escribir en el mismo idioma ".

Lograr esto, los investigadores hicieron uso de una técnica llamada aprendizaje de autómatas limitados. La técnica utiliza una combinación de diferentes análisis de programas para producir una máquina de estado que es equivalente en función al código original y susceptible de aceleración con FPGA. Esencialmente, su sistema lee el código que se le da, aprende la funcionalidad del código, y escribe una descripción de hardware de este comportamiento para enviar al acelerador.

En un artículo presentado sobre el trabajo, demostraron su técnica en una clase de funciones, granos de cuerda, que manejan operaciones de búsqueda y comparación realizadas en texto.

"Siempre que busque en un documento de texto, estás usando una de las formas más primitivas de estos núcleos de cadena, ", dice Angstadt. Pero pueden ser mucho más complejas:las funciones son fundamentales para aplicaciones tan diversas como la detección de spam, análisis genético, recomendaciones de productos, y física de partículas.

Ejecutar AutomataSynth en un conjunto de referencia de funciones de cadena del mundo real escritas para trabajar con CPU, el equipo descubrió que podía aprender diseños de hardware totalmente equivalentes en el 72% de los casos y aproximaciones cercanas en otro 11%.

La aplicación de esta técnica a otras clases de funciones sigue siendo un problema abierto para seguir trabajando, pero Angstadt confía en que se pueda utilizar de forma amplia.

"Nuestra investigación indica que, aunque existen muchos tipos de funciones además de las que apoyamos, hay más aplicaciones de las que creemos que se pueden reescribir como núcleos de cadena, ", dice Angstadt." Por lo tanto, es posible que aún podamos aplicar técnicas similares para admitir más tipos de código ".

Si tiene éxito, pudimos ver que los FPGA se convierten en un componente estándar para la computación de propósito general.

Los investigadores presentaron sus hallazgos en el documento "Aceleración de núcleos de cadenas heredados a través del aprendizaje de autómatas limitados, "aceptado por la Conferencia 2020 de Soporte Arquitectónico para Lenguajes de Programación y Sistemas Operativos (ASPLOS).