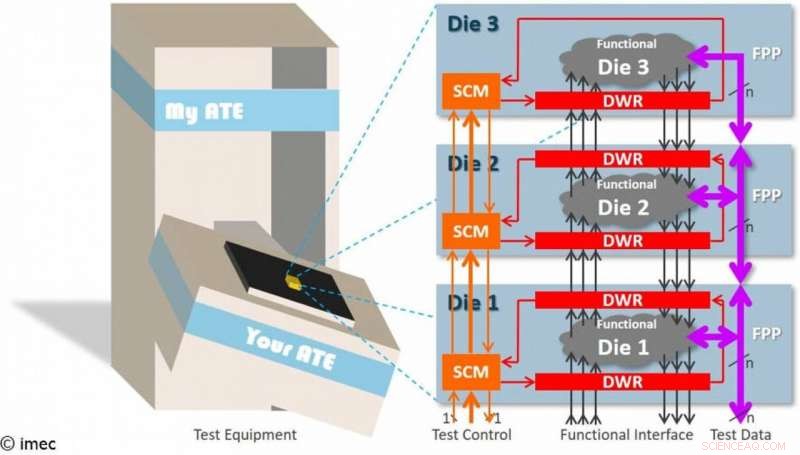

Sección transversal conceptual de un 3D-IC que consta de tres matrices apiladas. El equipo de prueba envía estímulos de prueba y recibe respuestas de prueba desde la interfaz externa del 3D-IC ubicada en la parte inferior de la pila. Los elementos de diseño para prueba IEEE Std 1838 ™ -2019 en los diversos troqueles forman una arquitectura de acceso de prueba consistente a través de la cual el equipo de prueba puede acceder a cada troquel en la pila. Crédito:IMEC

Esta semana, IMEC, un centro de investigación e innovación líder en el mundo en nanoelectrónica y tecnologías digitales, anunció que IEEE Std 1838TM-2019, recientemente aprobado por la IEEE Standards Association, se incluirá en la Biblioteca digital IEEE Xplore a partir de febrero de 2020. El nuevo estándar permite a los fabricantes de matrices diseñar matrices que, si cumple con esta norma, constituir, una vez apilado en un 3-D-IC por un integrador de pila, una arquitectura de acceso de prueba consistente a nivel de pila. El esfuerzo de estandarización del 3-D-DfT (diseño para prueba) fue iniciado por IMEC.

Los 3-D-IC explotan la dimensión vertical para una mayor integración apilando troqueles uno encima del otro como una forma de mantener el impulso de la Ley de Moore. Eric Beyne, miembro y director del programa de integración de sistemas 3-D en IMEC, dice, "Los avances en las tecnologías de procesamiento de obleas y ensamblaje de pilas están creando una gran cantidad de arquitecturas de pilas diferentes. Esto provoca un fuerte aumento en el número de momentos potenciales en los que se pueden ejecutar las pruebas para detectar defectos de fabricación:pre-unión (antes de apilar), mid-bond (en pilas parciales), post-bond (en pilas completas), y prueba final (en 3-D-IC empaquetados). El equipo de prueba se pone en contacto con los circuitos integrados a través de su interfaz externa a través de las agujas de la sonda o en el enchufe de prueba. En una pila de dados, esa interfaz externa normalmente reside en la matriz inferior de la pila. Para que el equipo de prueba pueda enviar estímulos de prueba y recibir respuestas de los distintos dados de la pila, se requiere la colaboración de los troqueles subyacentes para proporcionar acceso de prueba al troquel que se está probando actualmente ".

Un grupo de trabajo de IEEE para estandarizar 3-D-DfT fue fundado en 2011 por Erik Jan Marinissen, director científico del IMEC en Lovaina, Bélgica y sirvió como su primer presidente. En años recientes, Adam Cron, ingeniero principal de I + D en el grupo de diseño de Synopsys, ha sido la fuerza impulsora como presidente actual del Grupo de Trabajo.

Amit Sanghani, vicepresidente de ingeniería en el grupo de diseño de Synopsys en Mountain View, California, Estados Unidos declaró:"3-D-IC es una tecnología importante para ofrecer la próxima ola de innovación a medida que la industria supera los 7 nm. Actualmente, la muerte puede provenir de diferentes proveedores con arquitecturas DfT inconexas.

El nuevo estándar consta de tres elementos principales. (1) DWR, el registro de envoltura de troqueles:escanee cadenas en el límite de cada troquel en la pila para permitir la prueba modular de las partes internas de cada troquel y de las interconexiones entre cada par de troqueles adyacentes. (2) SCM, el mecanismo de control en serie:un mecanismo de control de prueba de un solo bit que transporta instrucciones a la pila para controlar los modos de prueba de las distintas envolvedoras de troqueles. (3) FPP, el puerto paralelo flexible opcional, es decir., un mecanismo de acceso de prueba escalable de múltiples bits para transportar eficientemente hacia arriba y hacia abajo en la pila de troqueles los grandes volúmenes de datos típicamente asociados con la prueba de producción. Si bien DWR y SCM se basan en los estándares DfT existentes, el FPP es verdaderamente novedoso para IEEE Std 1838.

Wolfgang Meyer, director senior de I + D del grupo en Cadence Design Systems en San José, California, NOSOTROS., dice, "Un estándar DfT como IEEE Std 1838 es importante para la industria. Los fabricantes de matrices saben lo que deben proporcionar, y los integradores de pila saben lo que pueden esperar. Es más, Los proveedores de EDA como Cadence pueden enfocar su soporte de herramientas en arquitecturas que cumplen con el nuevo estándar. Es bueno que haya cierta escalabilidad definida por el usuario con el estándar, ya que el campo 3-D-IC es tan amplio; un estándar rígido de 'talla única' no funcionaría ".

Junlin Huang, gerente de un equipo de DfT de 150 personas de HiSilicon en Shenzhen, Porcelana, dice, "Por año, Hacemos inserción DfT y generación automática de patrones de prueba (ATPG) para decenas de diseños de chips digitales muy grandes y complejos en las tecnologías más avanzadas. Ahora, Estos productos comienzan a usar tecnología 3-D y mi equipo de DfT debe estar listo para manejar los desafíos asociados de DfT y ATPG. IEEE Std 1838 nos ayudará con esa tarea ".

A partir de febrero de 2020, el nuevo estándar IEEE Std 1838 estará disponible a través de IEEE Xplore para los suscriptores de los estándares IEEE, así como para todos los demás.