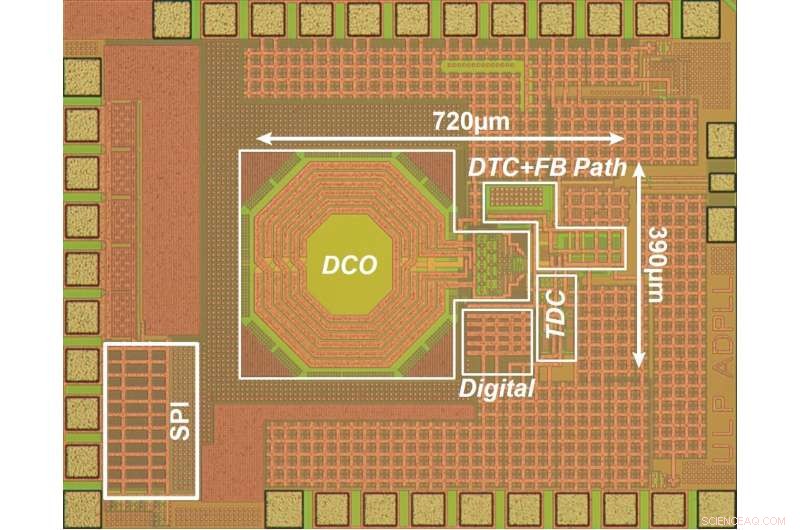

El DPLL de N fraccional propuesto ocupa un área de 0,25 mm 2 en CMOS de 65 nanómetros. Crédito:Kenichi Okada

Los científicos del Instituto de Tecnología de Tokio han desarrollado un sintetizador de frecuencia de bucle de bloqueo de fase (PLL) avanzado que puede reducir drásticamente el consumo de energía. Este PLL digital podría ser un bloque de construcción atractivo para Bluetooth Low Energy (BLE) y otras tecnologías inalámbricas para admitir una amplia gama de aplicaciones de Internet de las cosas (IoT).

Como componente clave de los sistemas de comunicación inalámbrica, Los sintetizadores de frecuencia deben satisfacer requisitos exigentes. Aunque los sintetizadores de frecuencia PLL analógicos han sido el estándar durante muchos años, Los ingenieros de la industria de IoT están prestando cada vez más atención a los llamados PLL digitales (DPLL) para lograr un funcionamiento de energía ultrabaja.

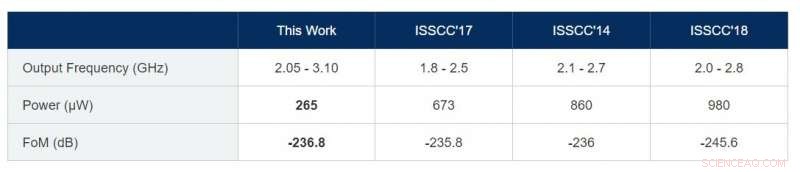

Kenichi Okada, profesor asociado en el Departamento de Ingeniería Eléctrica y Electrónica del Instituto de Tecnología de Tokio y su grupo ahora informan un DPLL fraccional-N que logra un consumo de energía de solo 265 microvatios (μW), una cifra que es menos de la mitad del consumo de energía más bajo alcanzado hasta la fecha (980 μW). (Tabla 1)

Los investigadores encontraron que el consumo total de energía podría reducirse en gran medida mediante el uso de un sistema de control de retroalimentación automático. "Esta ruta de retroalimentación de conmutación automática consume una potencia de 68 μW, lo que conduce a un consumo de energía de 265 μW para todo el DPLL, "Dice Okada.

El prometedor DPLL podría utilizarse como componente para procesadores, memorias y una amplia gama nueva de dispositivos de IoT que se espera que sean rentables y ecológicos al funcionar con energía ultrabaja. Okada señala que los primeros experimentos muestran que el DPLL podría extender la vida útil de la batería cuatro veces.

Los científicos del Instituto de Tecnología de Tokio han desarrollado un sintetizador de frecuencia de bucle de bloqueo de fase (PLL) avanzado que puede reducir drásticamente el consumo de energía. Este PLL digital podría ser un bloque de construcción atractivo para Bluetooth Low Energy (BLE) y otras tecnologías inalámbricas para admitir una amplia gama de aplicaciones de Internet de las cosas (IoT). Crédito:Kenichi Okada

Este documento se basa parcialmente en los resultados obtenidos de un proyecto encargado por la New Energy and Industrial Technology Development Organisation (NEDO).

Este trabajo se presenta en la sesión de Sintetizadores de frecuencia en la Conferencia Internacional de Circuitos de Estado Sólido de 2019 (ISSCC), el foro anual líder en el mundo sobre circuitos de estado sólido y sistemas en un chip.