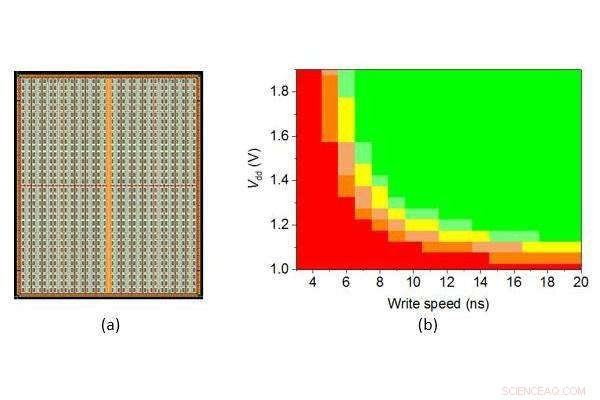

(a) Imagen de maqueta de STT-MRAM de 128 Mbit de densidad. (b) Gráfico de Shmoo para la velocidad de escritura frente al voltaje de suministro, que muestra la tasa de bits de operación medida a cada velocidad y voltaje en gradación de color. Crédito:Universidad de Tohoku

Un equipo de investigación dirigido por el profesor Tetsuo Endoh en la Universidad de Tohoku, ha desarrollado con éxito una memoria de acceso aleatorio magnetorresistiva de par de transferencia de giro de densidad de 128 Mb (STT-MRAM) con una velocidad de escritura de 14 ns para su uso en aplicaciones de memoria integradas, como caché en IoT e IA. Esta es actualmente la velocidad de escritura más rápida del mundo para aplicaciones de memoria integrada con una densidad superior a 100 Mb y allanará el camino para la producción en masa de STT-MRAM de gran capacidad.

STT-MRAM es capaz de funcionar a alta velocidad y consume muy poca energía, ya que retiene los datos incluso cuando está apagado. Debido a estas características, STT-MRAM está ganando terreno como tecnología de próxima generación para aplicaciones como la memoria integrada, memoria principal y lógica. Tres grandes plantas de fabricación de semiconductores han anunciado que la producción en masa de riesgo comenzará en 2018.

Como la memoria es un componente vital de los sistemas informáticos, dispositivos de mano y almacenamiento, su rendimiento y fiabilidad son de gran importancia para las soluciones de energía verde.

La capacidad actual de STT-MRAM oscila entre 8Mb-40 Mb. Pero para que STT-MRAM sea más práctico, es necesario aumentar la densidad de la memoria. El equipo del Centro de Sistemas Electrónicos Integrados Innovadores (CIES) ha aumentado la densidad de memoria de STT-MRAM mediante el desarrollo intensivo de STT-MRAM en los que las uniones de túnel magnéticas (MTJ) se integran con CMOS. Esto reducirá significativamente el consumo de energía de la memoria integrada, como la memoria caché y eFlash.

Los MTJ se miniaturizaron mediante una serie de desarrollos de procesos. Para reducir el tamaño de memoria necesario para STT-MRAM de mayor densidad, los MTJ se formaron directamente sobre orificios, pequeñas aberturas que permiten una conexión conductora entre las diferentes capas de un dispositivo semiconductor. Al utilizar la celda de memoria de tamaño reducido, el grupo de investigación ha diseñado STT-MRAM de 128 Mb de densidad y ha fabricado un chip.

En el chip fabricado, los investigadores midieron una velocidad de escritura de submatriz. Como resultado, El funcionamiento a alta velocidad con 14ns se demostró con un voltaje de suministro de energía bajo de 1,2 V.Hasta la fecha, esta es la operación de velocidad de escritura más rápida en un chip STT-MRAM con una densidad de más de 100 Mb en el mundo.