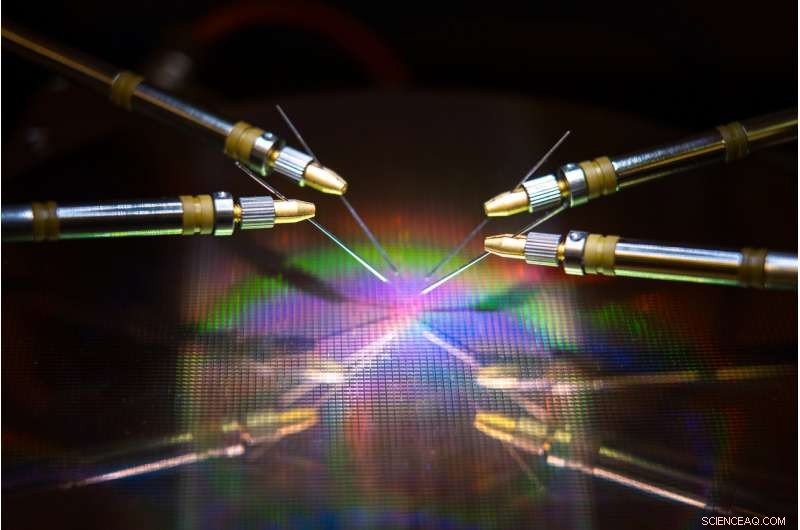

Un equipo dirigido por UC San Diego ha desarrollado hardware y algoritmos que podrían reducir el uso de energía y el tiempo al entrenar una red neuronal. Crédito:David Baillot / UC San Diego Jacobs School of Engineering

Un equipo dirigido por la Universidad de California en San Diego ha desarrollado un enfoque de codiseño de hardware y software inspirado en la neuroinstrucción que podría hacer que el entrenamiento de redes neuronales sea más eficiente y rápido en términos de energía. Su trabajo podría algún día hacer posible entrenar redes neuronales en dispositivos de bajo consumo como teléfonos inteligentes, portátiles y dispositivos integrados.

El avance se describe en un artículo publicado recientemente en Comunicaciones de la naturaleza .

Entrenamiento de redes neuronales para realizar tareas como reconocer objetos, navegar en coches autónomos o jugar a juegos consume mucha potencia informática y tiempo. Por lo general, se requieren computadoras grandes con cientos o miles de procesadores para aprender estas tareas, y los tiempos de formación pueden durar desde semanas hasta meses.

Esto se debe a que realizar estos cálculos implica transferir datos de un lado a otro entre dos unidades separadas, la memoria y el procesador, y esto consume la mayor parte de la energía y el tiempo durante el entrenamiento de la red neuronal. dijo el autor principal Duygu Kuzum, profesor de ingeniería eléctrica e informática en la Escuela de Ingeniería Jacobs de UC San Diego.

Para abordar este problema, Kuzum y su laboratorio se asociaron con Adesto Technologies para desarrollar hardware y algoritmos que permiten que estos cálculos se realicen directamente en la unidad de memoria. eliminando la necesidad de mezclar datos repetidamente.

"Estamos abordando este problema desde dos extremos, el dispositivo y los algoritmos, para maximizar la eficiencia energética durante el entrenamiento de redes neuronales, "dijo el primer autor Yuhan Shi, un doctorado en ingeniería eléctrica estudiante del grupo de investigación de Kuzum en UC San Diego.

El componente de hardware es un tipo de tecnología de memoria no volátil de gran eficiencia energética:una matriz de RAM de puente conductor subcuántico de 512 kilobits (CBRAM). Consume de 10 a 100 veces menos energía que las tecnologías de memoria líderes en la actualidad. El dispositivo se basa en la tecnología de memoria CBRAM de Adesto; se ha utilizado principalmente como un dispositivo de almacenamiento digital que solo tiene estados '0' y '1', pero Kuzum y su laboratorio demostraron que se puede programar para tener múltiples estados analógicos para emular sinapsis biológicas en el cerebro humano. Este llamado dispositivo sináptico se puede utilizar para realizar computación en memoria para el entrenamiento de redes neuronales.

"La memoria en chip en los procesadores convencionales es muy limitada, por lo que no tienen la capacidad suficiente para realizar la computación y el almacenamiento en el mismo chip. Pero en este enfoque, Tenemos una matriz de memoria de alta capacidad que puede realizar cálculos relacionados con el entrenamiento de redes neuronales en la memoria sin transferir datos a un procesador externo. Esto permitirá una gran mejora del rendimiento y reducirá el consumo de energía durante el entrenamiento. "dijo Kuzum.

Kuzum, que está afiliado al Center for Machine-Integrated Computing and Security en UC San Diego, lideró los esfuerzos para desarrollar algoritmos que pudieran mapearse fácilmente en esta matriz de dispositivos sinápticos. Los algoritmos proporcionaron aún más ahorro de energía y tiempo durante el entrenamiento de la red neuronal.

El enfoque utiliza un tipo de red neuronal energéticamente eficiente, llamada red neuronal de picos, para implementar el aprendizaje no supervisado en el hardware. Además de eso, El equipo de Kuzum aplica otro algoritmo de ahorro de energía que desarrollaron llamado "poda suave, "lo que hace que el entrenamiento de redes neuronales sea mucho más eficiente energéticamente sin sacrificar mucho en términos de precisión.

Yuhan Shi configura la matriz de dispositivos sinápticos para realizar pruebas. Crédito:Universidad de California - San Diego

Algoritmos de ahorro de energía

Las redes neuronales son una serie de capas conectadas de neuronas artificiales, donde la salida de una capa proporciona la entrada a la siguiente. La fuerza de las conexiones entre estas capas está representada por lo que se denominan "pesos". El entrenamiento de una red neuronal se ocupa de actualizar estos pesos.

Las redes neuronales convencionales gastan mucha energía para actualizar continuamente cada uno de estos pesos. Pero al aumentar las redes neuronales, solo se actualizan los pesos que están vinculados a las neuronas en punta. Esto significa menos actualizaciones, lo que significa menos potencia y tiempo de cálculo.

La red también realiza lo que se llama aprendizaje no supervisado, lo que significa que esencialmente puede entrenarse a sí mismo. Por ejemplo, si la red muestra una serie de dígitos numéricos escritos a mano, Descubrirá cómo distinguir entre ceros, unos, dos etc. Un beneficio es que no es necesario capacitar a la red en ejemplos etiquetados, lo que significa que no es necesario que se le diga que está viendo un cero, uno o dos, lo que resulta útil para aplicaciones autónomas como la navegación.

Para hacer que el entrenamiento sea aún más rápido y más eficiente energéticamente, El laboratorio de Kuzum desarrolló un nuevo algoritmo que denominaron "poda suave" para implementar con la red neuronal de picos sin supervisión. La poda suave es un método que encuentra pesos que ya han madurado durante el entrenamiento y luego los establece en un valor constante distinto de cero. Esto evita que se actualicen durante el resto del entrenamiento, lo que minimiza la potencia de cálculo.

La poda suave se diferencia de los métodos de poda convencionales porque se implementa durante el entrenamiento, en lugar de después. También puede conducir a una mayor precisión cuando una red neuronal pone a prueba su entrenamiento. Normalmente en poda, los pesos redundantes o sin importancia se eliminan por completo. La desventaja es que cuantas más pesas podes, cuanto menos precisa sea la red durante las pruebas. Pero la poda suave solo mantiene estos pesos en un entorno de baja energía, por lo que todavía están disponibles para ayudar a que la red funcione con mayor precisión.

Co-diseño de hardware-software para la prueba

El equipo implementó la red neuronal de picos no supervisada neuroinspirada y el algoritmo de poda suave en la matriz de dispositivos sinápticos CBRAM subcuánticos. Luego entrenaron a la red para clasificar dígitos escritos a mano de la base de datos MNIST.

En pruebas, la red clasificó los dígitos con una precisión del 93 por ciento, incluso cuando hasta el 75 por ciento de los pesos se recortaron suavemente. En comparación, la red funcionó con menos del 90 por ciento de precisión cuando solo el 40 por ciento de los pesos se podaron utilizando métodos de poda convencionales.

En términos de ahorro de energía, El equipo estima que su enfoque de codiseño de hardware-software inspirado en neuroinstrucciones puede eventualmente reducir el uso de energía durante el entrenamiento de redes neuronales en dos o tres órdenes de magnitud en comparación con el estado de la técnica.

"Si comparamos el nuevo hardware con otras tecnologías de memoria similares, estimamos que nuestro dispositivo puede reducir el consumo de energía de 10 a 100 veces, luego, el codiseño de nuestro algoritmo lo reduce en otros 10. En general, podemos esperar una ganancia de cien a mil veces en términos de consumo de energía siguiendo nuestro enfoque, "dijo Kuzum.

Avanzando Kuzum y su equipo planean trabajar con empresas de tecnología de memoria para hacer avanzar este trabajo a las siguientes etapas. Su objetivo final es desarrollar un sistema completo en el que las redes neuronales se puedan entrenar en la memoria para realizar tareas más complejas con presupuestos de tiempo y energía muy bajos.