El equipo de NUS Green IC:Dr. Orazio Aiello (izquierda) y profesor asociado Massimo Alioto (derecha). Crédito:Universidad Nacional de Singapur

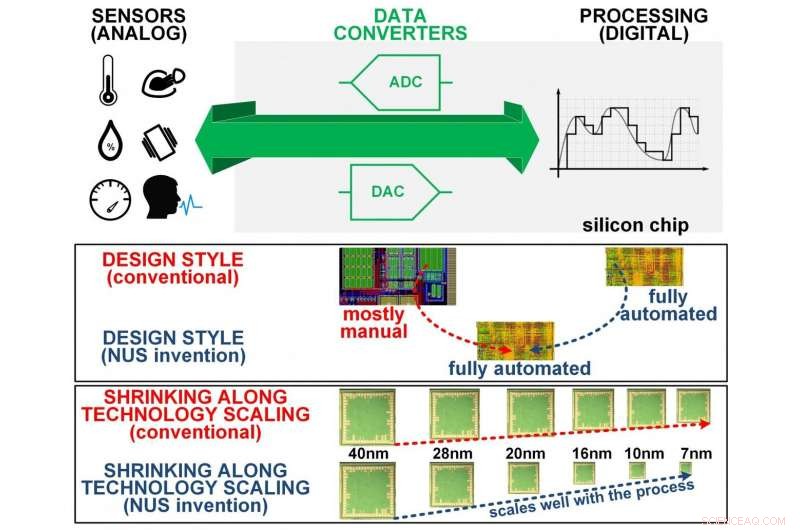

El grupo de investigación Green IC en el Departamento de Ingeniería Eléctrica e Informática de la Facultad de Ingeniería de la Universidad Nacional de Singapur (NUS) inventó una nueva clase de convertidores de digital a analógico (DAC) y analógico a digital (ADC) que pueden estar completamente diseñado con una metodología de diseño digital totalmente automatizada, gracias a su arquitectura totalmente digital (Fig. 1).

En comparación con las arquitecturas y metodologías analógicas tradicionales, el tiempo de respuesta del diseño de estas novedosas interfaces de sensor se reduce de meses a horas. La drástica reducción en el esfuerzo de diseño es muy beneficiosa en los sistemas de silicio sensibles a los costos, como sensores para Internet de las cosas (IoT). La nueva arquitectura del convertidor de datos también tiene una complejidad muy baja, reducir el área de silicio y, por lo tanto, el costo de fabricación en al menos 30 veces, en comparación con los diseños convencionales.

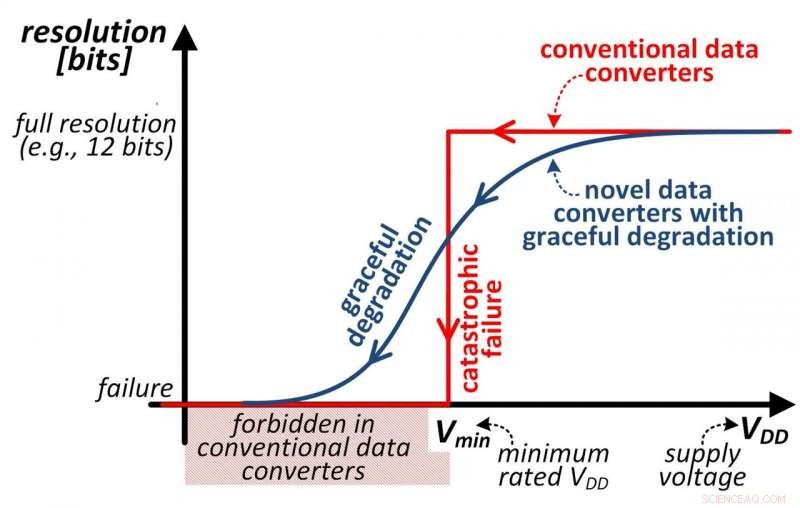

Estos nuevos convertidores de datos también exhiben la capacidad sin precedentes de degradar con gracia la fidelidad de la señal cuando su voltaje de suministro o frecuencia de reloj experimentan amplias fluctuaciones (Fig. 2). Tales fluctuaciones son comunes en los sensores de IoT de recolección de energía, siendo que la energía obtenida del entorno circundante (por ejemplo, célula solar) es muy errático. Sucesivamente, esto permite el monitoreo ininterrumpido de la señal del sensor incluso en condiciones desfavorables de energía recolectada, y sin regulación de voltaje. En lugar de, Los convertidores de datos tradicionales sufren una degradación catastrófica de la resolución cuando la tensión de alimentación está por debajo de su valor nominal mínimo Vmin (o la frecuencia supera su valor nominal máximo) como en la Fig.2, por lo tanto, se necesitan circuitos que consuman mucha energía para regular el voltaje y la frecuencia.

La investigación se llevó a cabo en colaboración con el profesor asociado Paolo Crovetti del Politecnico di Torino en Italia, y cuenta con el apoyo del Ministerio de Educación de Singapur y la Comisión de la UE.

Interfaces de sensor más pequeñas, más simple y rápido de diseñar

"Nuestra investigación transforma el diseño tradicionalmente analógico y en su mayoría manual de convertidores de datos en un diseño digital totalmente automatizado, reducir el área de silicio en un orden de magnitud y el tiempo de diseño en dos órdenes de magnitud, Permitir que las empresas de semiconductores sean competitivas en cuanto a costos mientras llegan a los mercados más rápido, "dijo el líder del equipo, profesor asociado Massimo Alioto, quien es del Departamento de Ingeniería Eléctrica e Informática de la Facultad de Ingeniería de NUS.

La falla catastrófica es reemplazada por una elegante degradación de la resolución en la nueva clase de convertidores de datos convencionales inventados por el equipo de NUS. Esto permite simplificar drásticamente el diseño del sistema, suprimiendo la necesidad de una regulación de voltaje precisa. Crédito:Universidad Nacional de Singapur

Él agregó, "Al ser digital, Nuestras interfaces de sensores se trasladan sin esfuerzo a través de tecnologías y aplicaciones de fabricación, y pueden sumergirse en circuitos digitales para evitar el esfuerzo tradicional que requiere su integración en un mismo chip de silicio ”(Fig. 1).

El equipo de NUS demostró el concepto a través de varios chips de silicio que implementan tanto DAC como ADC con un área extremadamente baja. Como ejemplo, Se ha demostrado un DAC de 12 bits fabricado con tecnología CMOS estándar de 40 nm con un área igual al diámetro de un mechón de cabello humano. Su facilidad inherente para el escalado de la tecnología hace que se reduzca aproximadamente otras 32 veces cuando se implementa en la tecnología más fina actualmente (7 nm).

Al mismo tiempo, Se ha demostrado que la invención de NUS permite convertidores de datos con altas resoluciones (hasta 16 bits), logrando al mismo tiempo simplicidad y compacidad de diseño.

Miembro del equipo Dr. Orazio Aiello, quien es investigador visitante en el Departamento, dijo, "Nuestro equipo ha introducido un nuevo paradigma de diseño que nos acerca a la visión definitiva de lo económico, dispositivos IoT ultracompactos y escalables por tecnología ".

La robustez sin precedentes aporta beneficios adicionales a nivel del sistema

La innovación NUS simplifica aún más el diseño del sistema integrado, aprovechando la capacidad sin precedentes para soportar fluctuaciones de voltaje y frecuencia muy sustanciales, relajando así los requisitos de precisión en la generación de tensión y frecuencia.

La falla catastrófica es reemplazada por una elegante degradación de la resolución en la nueva clase de convertidores de datos convencionales inventados por los investigadores de NUS. Crédito:Universidad Nacional de Singapur

En efecto, Los convertidores de datos convencionales que operan a un voltaje de suministro por debajo de su valor nominal mínimo (o frecuencia de reloj excesiva) experimentan fallas catastróficas, y por lo tanto no realiza su función prevista (Fig. 2). De lo contrario, Los innovadores convertidores de datos inventados por el equipo de NUS exhiben una elegante degradación de la resolución y fidelidad de la señal cuando el voltaje de suministro o la frecuencia del reloj exceden su rango permitido. Como ejemplo, Se demostró que un DAC diseñado para 1 V funciona correctamente a la mitad de este voltaje, mientras degrada su resolución en solo 1 bit cuando el voltaje de suministro se reduce en un sustancial 0.3V.

El profesor adjunto Alioto dijo:"La capacidad de tener una degradación de resolución elegante bajo voltaje y sobreescala de frecuencia elimina la necesidad de soluciones de circuito complejas que regulen con precisión el voltaje de suministro y la frecuencia de reloj que utilizan los convertidores de datos. En otras palabras, nuestros convertidores de datos son más sencillos de diseñar, y también simplificar el sistema en el que se emplean ".

Próximos pasos

El equipo está trabajando actualmente en un paradigma novedoso que convierte subsistemas de silicio tradicionalmente analógicos y de diseño intensivo en diseños digitales basados en celdas estándar que están respaldados por flujos de diseño totalmente automatizados. empujando los límites del diseño clásico asistido digitalmente. Este estudio de investigación involucra varios subsistemas fundamentales como amplificadores, osciladores, referencias de tensión y corriente, y muchos otros.

El equipo de investigación tiene como objetivo transformar la forma en que se diseñan los sistemas integrados, permitiendo ultrarrápido, Diseño ultracompacto y de tecnología portátil de sistemas completos.