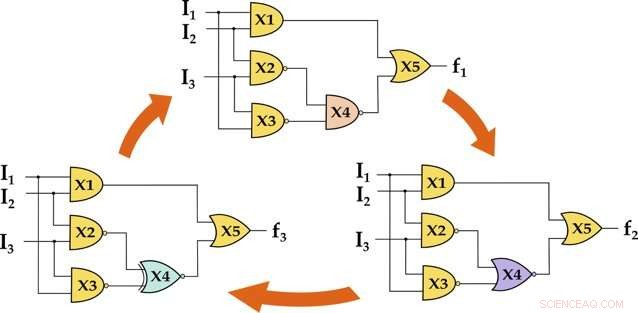

La globalización de la cadena de suministro de CI ha inducido vulnerabilidades en varias etapas de la producción de CI. Aquí, las etapas de las zonas rojas no son de confianza y pueden ser explotadas por un atacante. Crédito:Rangarajan et al.

En años recientes, Las amenazas a la seguridad centradas en el hardware han surgido en diferentes etapas de la cadena de suministro de circuitos integrados (IC). Esto ha permitido la proliferación de varios ataques maliciosos, como la piratería de la propiedad intelectual (PI), sobreproducción ilegal de circuitos integrados, e inserción de troyanos de hardware.

De todas las defensas existentes contra la piratería de la propiedad intelectual, Hasta ahora, solo se ha descubierto que el bloqueo lógico ofrece una protección efectiva de extremo a extremo. Para abordar estos desafíos, un equipo de investigación del Laboratorio del Centro de Ciberseguridad y Nanoelectrónica Cuántica de la Universidad de Nueva York ha desarrollado un enfoque de camuflaje dinámico para frustrar la ingeniería inversa de IP en todas las etapas de la cadena de suministro.

"La globalización de la cadena de suministro de circuitos integrados ha dado lugar a la subcontratación de varios pasos de la producción de chips microelectrónicos, "Nikhil Rangarajan, uno de los investigadores que realizó el estudio, dicho TechXplore . "Por lo general, los chips se diseñan y / o se adquieren en un país, fabricado en otro, y finalmente probado y empaquetado en otro lugar. Esta cadena mundial abre muchas oportunidades para que los atacantes roben la IP subyacente, disfrutar de la sobreproducción, o incluso insertar modificaciones maliciosas conocidas como troyanos de hardware ".

Según estimaciones, la industria de los semiconductores pierde miles de millones de dólares cada año debido al robo de IP. Para mitigar este daño, la investigación llevada a cabo por Rangarajan y sus colegas se centra específicamente en prevenir el robo de propiedad intelectual.

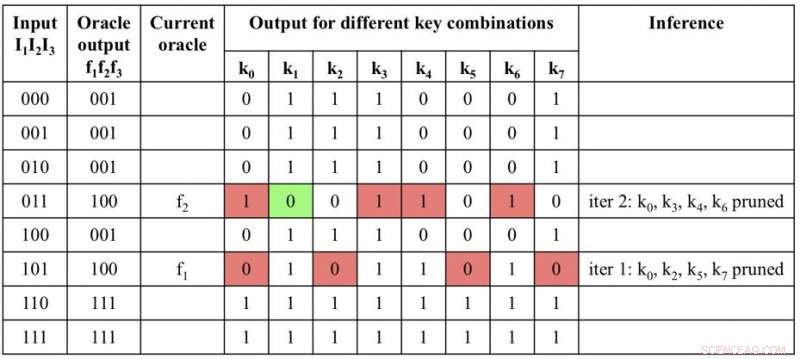

Conmutación dinámica de circuitos polimórficos sobre la marcha. Crédito:Rangarajan et al.

"La inspiración de nuestra idea provino de la naturaleza, donde algunos animales como el pulpo pueden cambiar su apariencia física para adaptarse a su entorno para evitar ser detectados por presas o depredadores, "Explicó Rangarajan." Pensamos:¿Por qué los circuitos electrónicos que buscamos proteger no pueden cambiar también dinámicamente para evitar ser detectados por un atacante? "

Mecanismos de defensa existentes para la prevención del robo de propiedad intelectual, como el camuflaje estático, requieren que el diseñador confíe en la fundición encargada para la fabricación del chip. De lo contrario, el modelo de amenaza ideado por Rangarajan y sus colegas supone que un atacante también podría residir dentro de la fundición o en la instalación de prueba, o potencialmente podría ser un usuario final.

"Al utilizar propiedades innatas como el polimorfismo, multifuncionalidad, y reconfigurabilidad posterior a la fabricación que ofrecen los dispositivos espintrónicos emergentes, como el dispositivo de órbita de giro magnetoeléctrico (MESO), pudimos lograr un camuflaje dinámico, "Satwik Patnaik, otro investigador involucrado en el estudio, dijo a TechXplore. "El polimorfismo está destinado a los medios particulares a través de los cuales el dispositivo puede implementar fácilmente diferentes funciones booleanas en tiempo de ejecución, donde la funcionalidad está determinada por un mecanismo de control interno o externo ".

En el esquema ideado por los investigadores, una fundición potencialmente maliciosa fabrica las puertas lógicas como "cajas negras, "que solo puede ser configurado por el diseñador una vez que se completa el proceso de fabricación. Esto evita que un atacante dentro de la fundición descifre la funcionalidad prevista del chip que se está fabricando, ya que aún no se ha configurado.

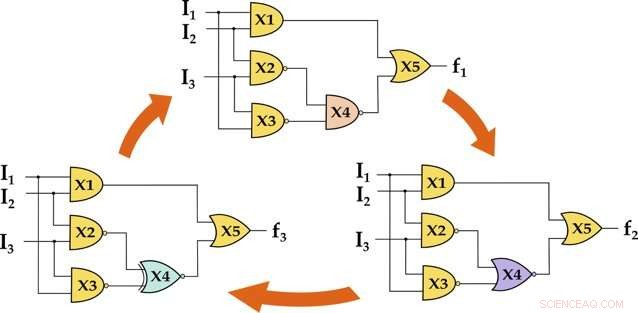

El camuflaje dinámico es posible con la ayuda de nuevas puertas espintrónicas como las puertas MESO. Estas puertas pueden implementar varias funcionalidades booleanas en un dispositivo y también pueden cambiar entre ellas durante el tiempo de ejecución. Crédito:Rangarajan et al.

"Esta propiedad de 'reconfiguración posterior a la fabricación' también permite la protección contra instalaciones de prueba que no son de confianza, ya que el chip puede configurarse para cualquier funcionalidad ficticia desconocida para un atacante y restaurarse a la verdadera funcionalidad una vez que se han llevado a cabo las pruebas, "Explicó Patnaik." En resumen, mientras que los trabajos previos en camuflaje IC son estáticos y deben confiar en la fundición, nuestro esquema no requiere que el diseñador confíe en la fundición o en las instalaciones de prueba ".

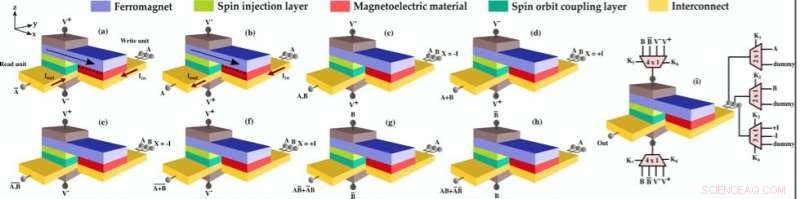

Los investigadores evaluaron la efectividad de su enfoque para contrarrestar los ataques de minería de datos de prueba de última generación, como HackTest, y análisis de canal lateral, donde los adversarios pretenden descifrar la funcionalidad de la IP. También exploraron su rendimiento con poderosos ataques de satisfacibilidad booleanos, incluyendo SAT y SAT aproximado (AppSAT), que suelen ser los preferidos por los usuarios finales.

Su enfoque de camuflaje dinámico arrojó resultados prometedores en todas estas pruebas. En el futuro, los investigadores creen que podría ayudar a frustrar a los atacantes dentro de fundiciones o instalaciones de prueba que no son de confianza.

"Nuestro esquema aprovecha las propiedades únicas de los dispositivos basados en espines, ", Explicó Rangarajan." Estas propiedades, especialmente polimorfismo, no se puede permitir con las tecnologías CMOS actuales, debido a las limitaciones fundamentales de los dispositivos CMOS. También queremos enfatizar que la noción general de camuflaje dinámico podría implementarse con otros dispositivos emergentes, siempre que tengan propiedades similares ".

Un ataque de satisfacibilidad booleano montado en un circuito camuflado dinámicamente puede generar fácilmente una clave incorrecta y engañar al atacante. Crédito:Rangarajan et al.

Para promover la implementación de su técnica de defensa, los investigadores también prevén una integración híbrida basada en CMOS-spin. Esta integración podría facilitar la adopción y aceptación de su esquema, así como de los dispositivos que lo soportan. Según los investigadores, varios estudios académicos se encaminan actualmente en direcciones similares.

Rangarajan y sus colegas ahora planean investigar las implicaciones de usar polimorfismo en tiempo de ejecución para proteger circuitos lógicos aproximados. que han ganado mucha tracción en los últimos años. Estos tipos de circuitos compensan la precisión de salida por una fuerte reducción en la disipación de potencia.

"Especialmente con la llegada de Internet-of-Things (IoT), Creemos que la protección de chips informáticos aproximados también es esencial, dado el hecho de que son ampliamente preferidos para su uso en sistemas que requieren un funcionamiento de baja potencia, ", Dijo Rangarajan." También planeamos evaluar la resistencia de nuestro esquema en otros escenarios de ataque, para ganar más confianza en nuestro enfoque ".

© 2018 Science X Network