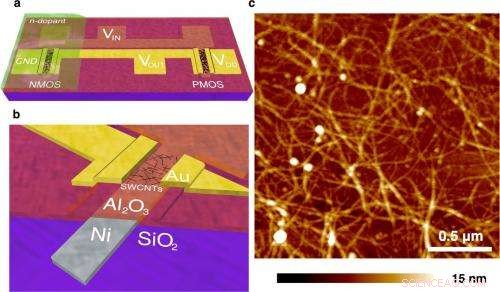

Ilustraciones de (a) el inversor CNT CMOS y (b) una sección transversal de un transistor CNT individual, incluyendo una compuerta de Ni de 25 nm de espesor que permite un consumo de energía ultrabajo. (c) Imagen de microscopía de fuerza atómica de la morfología de la película CNT en la región del canal del transistor. Crédito:Geier, et al. © 2013 Sociedad Química Estadounidense

(Phys.org) —Los investigadores han demostrado un nuevo dispositivo lógico basado en nanotubos de carbono (CNT) que consume solo 0,1 nanovatios (nW) en sus estados estáticos ON y OFF, que representa el valor informado más bajo en 3 órdenes de magnitud para los dispositivos lógicos CMOS basados en CNT. El dispositivo podría servir como un bloque de construcción para áreas grandes, Circuitos lógicos CNT de potencia ultrabaja que se pueden utilizar para realizar una variedad de aplicaciones nanoelectrónicas.

Los investigadores, Michael L. Geier, et al., en la Universidad Northwestern en Evanston, Illinois, y la Universidad de Minnesota en Minneapolis, han publicado su artículo sobre la lógica CNT de subnanvatios en un número reciente de Nano letras .

"Un circuito integrado moderno tiene más de mil millones de transistores, "el coautor Mark C. Hersam, Catedrático de Ciencia e Ingeniería de Materiales, Química, y Medicina en la Universidad Northwestern, dicho Phys.org . "Como consecuencia, la disipación de energía por transistor debe ser muy baja para que todo el circuito tenga un consumo de energía razonable. De hecho, En general, se acepta que el consumo de energía es el factor limitante clave para lograr mayores aumentos en la complejidad (es decir, número de transistores) en circuitos integrados ".

Como explican los investigadores, Una de las mayores ventajas de la arquitectura CMOS es que tiene un consumo de energía intrínsecamente bajo. Este beneficio surge del hecho de que, a diferencia de otras arquitecturas lógicas, uno de los dos tipos de transistores (tipo p o tipo n) se apaga en condiciones de estado estable en cada puerta lógica de los dispositivos CMOS.

Para aprovechar al máximo este potencial de consumo de energía extremadamente bajo, los transistores de tipo py de tipo n deben tener tensiones de umbral bien sintonizadas con precisión y bien separadas, que son los niveles de voltaje que determinan si el dispositivo está encendido o apagado. Hasta aquí, este problema de los voltajes de umbral no se ha abordado, y los investigadores lo identificaron aquí como el desafío clave que limita la realización de componentes electrónicos CMOS basados en CNT altamente integrados.

En su estudio, Los investigadores utilizaron una estructura de puerta de metal para lograr voltajes de umbral simétricos y claramente separados para transistores CNT de tipo py de tipo n, resultando en un consumo de energía ultrabajo. En los estados estáticos, en el que el dispositivo está ENCENDIDO o APAGADO, el consumo de energía es inferior a 0,1 nW. En el punto medio del estado de transferencia, cuando tanto los transistores de tipo p como los de tipo n están simultáneamente en el estado ON, el voltaje alcanza su pico a 10 nW.

Al conectar varios transistores CNT en varias configuraciones, los investigadores demostraron inversor, Puertas lógicas NAND y NOR. En el futuro, estas puertas se pueden integrar en circuitos complejos, donde pueden proporcionar un consumo de energía estática de subnanowatt junto con las otras ventajas de los CNT, como la capacidad de procesamiento y la flexibilidad de la solución.

"Ahora estamos trabajando para hacer circuitos más complicados, donde tendremos sustancialmente más transistores y puertas lógicas en cascada, ", Dijo Hersam." También tenemos interés en combinar nanotubos de carbono con otros materiales nanoelectrónicos emergentes en nuestro laboratorio (por ejemplo, disulfuro de molibdeno [MoS 2 ]). "

© 2013 Phys.org. Reservados todos los derechos.