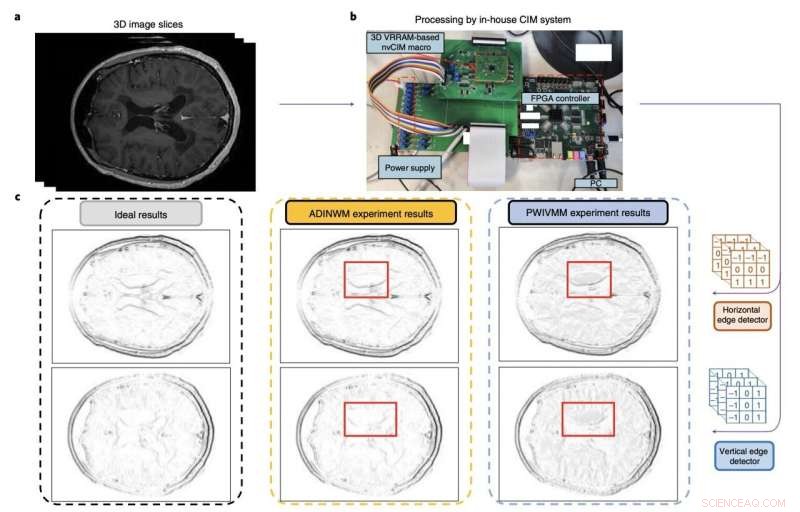

Figura que resume la evaluación y el rendimiento de la macro de computación en memoria de los investigadores. Crédito:Huo et al (Nature Electronics , 2022).

Las arquitecturas de aprendizaje automático basadas en redes neuronales convolucionales (CNN) han demostrado ser muy valiosas para una amplia gama de aplicaciones, que van desde la visión artificial hasta el análisis de imágenes y el procesamiento o generación de lenguaje humano. Sin embargo, para abordar tareas más avanzadas, estas arquitecturas se están volviendo cada vez más complejas y exigentes desde el punto de vista computacional.

En los últimos años, muchos ingenieros electrónicos de todo el mundo han intentado desarrollar dispositivos que puedan admitir el almacenamiento y la carga computacional de arquitecturas complejas basadas en CNN. Esto incluye dispositivos de memoria más densos que pueden admitir grandes cantidades de pesos (es decir, los parámetros entrenables y no entrenables considerados por las diferentes capas de CNN).

Investigadores de la Academia de Ciencias de China, el Instituto de Tecnología de Beijing y otras universidades de China han desarrollado recientemente un nuevo sistema de computación en memoria que podría ayudar a ejecutar modelos más complejos basados en CNN de manera más efectiva. Su componente de memoria, presentado en un artículo publicado en Nature Electronics , se basa en macros de computación en memoria no volátiles hechas de matrices de memristores 3D.

"Escalar dichos sistemas a matrices 3D podría proporcionar un mayor paralelismo, capacidad y densidad para las operaciones necesarias de multiplicación de matrices vectoriales", escribieron Qiang Huo y sus colegas en su artículo. "Sin embargo, escalar a tres dimensiones es un desafío debido a problemas de fabricación y variabilidad del dispositivo. Informamos una macro de computación en memoria no volátil de dos kilobits que se basa en una memoria de acceso aleatorio resistiva vertical tridimensional fabricada con un 55 nm proceso complementario de semiconductores de óxido de metal".

Las memorias resistivas de acceso aleatorio, o RRAM, son dispositivos de almacenamiento no volátiles (es decir, que retienen datos incluso después de cortes en la fuente de alimentación) basados en memristores. Los memristores son componentes electrónicos que pueden limitar o regular el flujo de corriente eléctrica en los circuitos, mientras registran la cantidad de carga que fluyó previamente a través de ellos.

Las RRAM esencialmente funcionan variando la resistencia a través de un memristor. Si bien estudios anteriores han demostrado el gran potencial de estos dispositivos de memoria, las versiones convencionales de estos dispositivos están separadas de los motores informáticos, lo que limita sus posibles aplicaciones.

Los dispositivos RRAM de cómputo en memoria fueron diseñados para superar esta limitación, incorporando los cómputos dentro de la memoria. Esto puede reducir en gran medida la transferencia de datos entre las memorias y los procesadores y, en última instancia, mejorar la eficiencia energética general del sistema.

El dispositivo de computación en memoria creado por Huo y sus colegas es una RRAM 3D con capas apiladas verticalmente y circuitos periféricos. Los circuitos del dispositivo se fabricaron con tecnología CMOS de 55 nm, la tecnología que sustenta la mayoría de los circuitos integrados del mercado actual.

Los investigadores evaluaron su dispositivo usándolo para llevar a cabo operaciones complejas y ejecutar un modelo para detectar bordes en escáneres cerebrales de resonancia magnética. El equipo entrenó sus modelos utilizando dos conjuntos de datos de IRM existentes para entrenar herramientas de reconocimiento de imágenes, conocidos como conjuntos de datos MNIST y CIFAR-10.

"Nuestra macro puede realizar operaciones de multiplicación de matriz vectorial en 3D con una eficiencia energética de 8,32 teraoperaciones por segundo por vatio cuando los datos de entrada, peso y salida son de 8,9 y 22 bits, respectivamente, y la densidad de bits es de 58,2 bits µm. –2 ", escribieron los investigadores en su artículo. "Mostramos que la macro ofrece una detección de bordes de resonancia magnética cerebral más precisa y una precisión de inferencia mejorada en el conjunto de datos CIFAR-10 que los métodos convencionales".

En las pruebas iniciales, el sistema RRAM vertical de computación en memoria creado por Huo y sus colegas logró resultados notables, superando los enfoques RRAM convencionales. En el futuro, podría resultar muy valioso para ejecutar modelos complejos basados en CNN de manera más eficiente desde el punto de vista energético, al tiempo que permite mejores precisiones y rendimientos.

© 2022 Red Ciencia X Una macro nvCIM de cuatro megabits para dispositivos de IA perimetrales