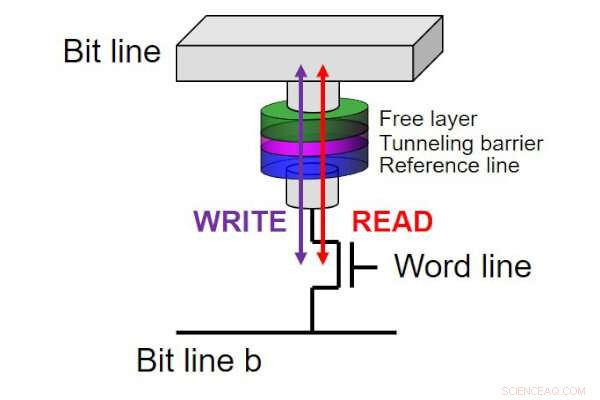

Esquema de la celda STT-MRAM (dispositivo de dos terminales). Crédito:CIES, Universidad de Tohoku

Investigadores de la Universidad de Tohoku han anunciado la demostración de una celda de memoria de acceso aleatorio magnetorresistivo de giro-órbita-par (SOT) de alta velocidad compatible con tecnología Si CMOS de 300 mm.

La demanda de circuitos integrados (IC) de bajo consumo y alto rendimiento ha ido en aumento a medida que la inteligencia artificial (IA) y los dispositivos de Internet de las cosas (IoT) se adoptan cada vez más. Con los CI actuales, Las memorias basadas exclusivamente en CMOS, como la memoria Flash incorporada (eFlash) y la memoria estática de acceso aleatorio (SRAM), son responsables de una alta proporción del consumo de energía. Para reducir el consumo de energía manteniendo un alto rendimiento, Se han desarrollado intensamente memorias magnetorresistivas de acceso aleatorio (MRAM). Los MRAM de par de transferencia de giro (STT-MRAM) son los MRAM más desarrollados. Las principales empresas de semiconductores han anunciado que están listas para la producción en masa de STT-MRAM para el reemplazo de eFlash.

Los investigadores tienen como objetivo reemplazar SRAM con MRAM. Para reemplazo de SRAM, MRAM debe lograr un funcionamiento a alta velocidad por encima de 500 MHz. Para satisfacer la demanda, un MRAM alternativo, Se propuso el llamado MRAM de par de giro en órbita (SOT-MRAM), que tiene varias ventajas para el funcionamiento a alta velocidad. Debido a estas ventajas, También se ha desarrollado SOT-MRAM; sin embargo, la mayoría de los estudios de laboratorio se centran en los fundamentos de los dispositivos SOT. Para realizar el reemplazo de SRAM por SOT-MRAM, es necesario para demostrar el alto rendimiento de la celda de memoria SOT-MRAM en un sustrato CMOS de 300 mm. Además, es necesario desarrollar el proceso de integración para SOT-MRAM, p.ej., tolerancia térmica frente al recocido a 400 ° C, que es un requisito del proceso de back-end-of-line CMOS estándar.

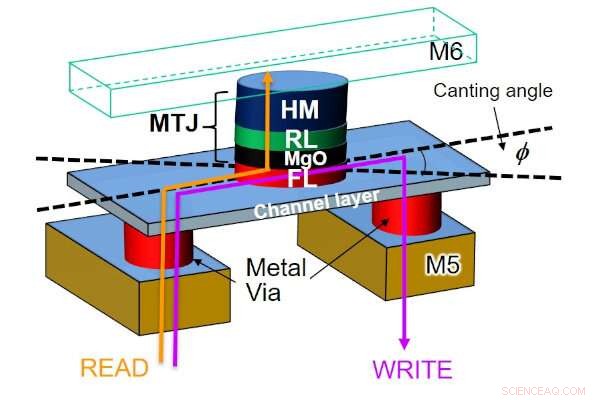

Un esquema de la celda SOT-MRAM (dispositivo de tres terminales) Crédito:CIES, Universidad de Tohoku

Una vista esquemática de la celda SOT-MRAM inclinada. Crédito:CIES, Universidad de Tohoku

El equipo de investigación dirigido por los profesores Tetsuo Endoh y Hideo Ohno, actual presidente de la Universidad de Tohoku, ha desarrollado un proceso de integración para dispositivos SOT compatibles con la tecnología CMOS de 55 nm y ha fabricado dispositivos SOT en sustratos CMOS de 300 mm. El dispositivo SOT recientemente desarrollado ha logrado simultáneamente una conmutación de alta velocidad hasta 0,35 ns y un factor de estabilidad térmica suficientemente alto (E / k B T 70) para las aplicaciones de memoria no volátil de alta velocidad con robustez frente al recocido a 400 ° C. Basado en este logro, el equipo de investigación integró el dispositivo SOT con transistores CMOS y finalmente demostró el funcionamiento a alta velocidad en celdas de memoria SOT-MRAM completas.

Estos logros han abordado los problemas para hacer que SOT-MRAM sea práctico para aplicaciones comerciales y, por lo tanto, ofrecer una forma de reemplazar SRAM con SOT-MRAM, lo que contribuirá a la realización de electrónica de alto rendimiento con bajo consumo de energía.

Los resultados se presentarán en la Reunión Internacional de Dispositivos Electrónicos IEEE 2019 en San Francisco, 7-11 de diciembre 2019.