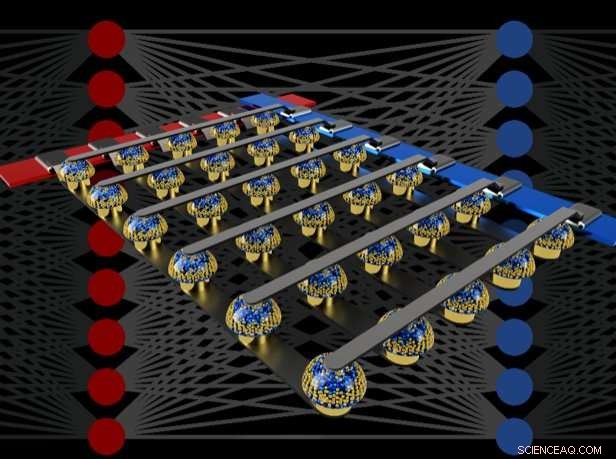

Los arreglos de barras cruzadas de memorias no volátiles pueden acelerar el entrenamiento de redes neuronales completamente conectadas al realizar cálculos en la ubicación de los datos. Crédito:IBM

Imagínese Inteligencia Artificial (IA) personalizada, donde su teléfono inteligente se vuelve más como un asistente inteligente:reconoce su voz incluso en una habitación ruidosa, comprender el contexto de diferentes situaciones sociales o presentar solo la información que sea realmente relevante para usted, extraídos de la avalancha de datos que llegan todos los días. Es posible que estas capacidades estén pronto a nuestro alcance, pero llegar allí requerirá poderoso, aceleradores de hardware de IA energéticamente eficientes.

En un artículo reciente publicado en Naturaleza , Nuestro equipo de IBM Research AI demostró un entrenamiento de redes neuronales profundas (DNN) con grandes conjuntos de dispositivos de memoria analógicos con la misma precisión que un sistema basado en una unidad de procesamiento gráfico (GPU). Creemos que este es un paso importante en el camino hacia el tipo de aceleradores de hardware necesarios para los próximos avances en IA. ¿Por qué? Porque entregar el Futuro de la IA requerirá expandir enormemente la escala de los cálculos de IA.

Los DNN deben hacerse más grandes y más rápidos, tanto en la nube como en el perímetro, y esto significa que la eficiencia energética debe mejorar drásticamente. Si bien mejores GPU u otros aceleradores digitales pueden ayudar hasta cierto punto, estos sistemas invierten inevitablemente mucho tiempo y energía en mover datos de la memoria al procesamiento y viceversa. Podemos mejorar tanto la velocidad como la eficiencia energética al realizar cálculos de IA en el dominio analógico con la ubicación de los datos, pero esto solo tiene sentido si las redes neuronales resultantes son tan inteligentes como las implementadas con hardware digital convencional.

Técnicas analógicas, que involucran señales continuamente variables en lugar de 0 y 1 binarios, tienen límites inherentes a su precisión, razón por la cual las computadoras modernas son generalmente computadoras digitales. Sin embargo, Los investigadores de IA han comenzado a darse cuenta de que sus modelos DNN todavía funcionan bien incluso cuando la precisión digital se reduce a niveles que serían demasiado bajos para casi cualquier otra aplicación informática. Por lo tanto, para DNN, es posible que la computación analógica también funcione.

Sin embargo, hasta ahora, nadie había probado de manera concluyente que tales enfoques analógicos pudieran hacer el mismo trabajo que el software actual que se ejecuta en hardware digital convencional. Es decir, ¿Se pueden realmente entrenar los DNN para alcanzar una precisión equivalente alta con estas técnicas? No tiene mucho sentido ser más rápido o más eficiente energéticamente en el entrenamiento de un DNN si las precisiones de clasificación resultantes siempre serán inaceptablemente bajas.

En nuestro periódico, Describimos cómo las memorias analógicas no volátiles (NVM) pueden acelerar de manera eficiente el algoritmo de "retropropagación" en el corazón de muchos avances recientes de la IA. Estas memorias permiten que las operaciones de "acumulación múltiple" utilizadas en estos algoritmos sean paralelizadas en el dominio analógico. en la ubicación de los datos de peso, utilizando la física subyacente. En lugar de grandes circuitos para multiplicar y sumar números digitales, simplemente pasamos una pequeña corriente a través de una resistencia a un cable, y luego conecte muchos de esos cables juntos para permitir que se acumulen las corrientes. Esto nos permite realizar muchos cálculos al mismo tiempo, en lugar de uno tras otro. Y en lugar de enviar datos digitales en viajes largos entre chips de memoria digital y chips de procesamiento, podemos realizar todos los cálculos dentro del chip de memoria analógica.

Sin embargo, debido a varias imperfecciones inherentes a los dispositivos de memoria analógicos actuales, Las demostraciones previas de entrenamiento DNN realizadas directamente en grandes arreglos de dispositivos NVM reales no lograron obtener precisiones de clasificación que coincidieran con las de las redes capacitadas por software.

Al combinar el almacenamiento a largo plazo en dispositivos de memoria de cambio de fase (PCM), actualización casi lineal de los condensadores semiconductores de óxido de metal complementario (CMOS) convencionales y técnicas novedosas para cancelar la variabilidad de dispositivo a dispositivo, refinamos estas imperfecciones y logramos precisiones DNN equivalentes al software en una variedad de redes diferentes. Estos experimentos utilizaron un enfoque mixto hardware-software, combinando simulaciones de software de elementos del sistema que son fáciles de modelar con precisión (como dispositivos CMOS) junto con la implementación completa de hardware de los dispositivos PCM. Era fundamental utilizar dispositivos de memoria analógicos reales para cada peso de nuestras redes neuronales, porque los enfoques de modelado para dispositivos tan novedosos con frecuencia no logran capturar la gama completa de variabilidad de dispositivo a dispositivo que pueden exhibir.

Usando este enfoque, Verificamos que los chips completos deberían ofrecer una precisión equivalente, y así hacer el mismo trabajo que un acelerador digital, pero más rápido y con menor potencia. Dados estos resultados alentadores, ya hemos comenzado a explorar el diseño de prototipos de chips aceleradores de hardware, como parte de un proyecto del IBM Research Frontiers Institute.

A partir de estos primeros esfuerzos de diseño, pudimos proporcionar, como parte de nuestro artículo de Nature, estimaciones iniciales del potencial de dichos chips basados en NVM para entrenar capas completamente conectadas, en términos de eficiencia energética computacional (28, 065 GOP / seg / W) y rendimiento por área (3.6 TOP / seg / mm2). Estos valores superan las especificaciones de las GPU actuales en dos órdenes de magnitud. Es más, Las capas totalmente conectadas son un tipo de capa de red neuronal para la que el rendimiento real de la GPU con frecuencia cae muy por debajo de las especificaciones clasificadas.

Este documento indica que nuestro enfoque basado en NVM puede ofrecer precisiones de entrenamiento equivalentes al software, así como mejoras de órdenes de magnitud en la aceleración y la eficiencia energética a pesar de las imperfecciones de los dispositivos de memoria analógica existentes. Los próximos pasos serán demostrar esta misma equivalencia de software en redes más grandes que requieren grandes Capas completamente conectadas, como las redes de memoria a corto plazo a largo plazo (LSTM) y unidades recurrentes cerradas (GRU) conectadas de forma recurrente, detrás de los avances recientes en la traducción automática. subtítulos y análisis de texto, y para diseñar, Implementar y perfeccionar estas técnicas analógicas en prototipos de aceleradores de hardware basados en NVM. Nuevas y mejores formas de memoria analógica, optimizado para esta aplicación, podría ayudar a mejorar aún más tanto la densidad del área como la eficiencia energética.