Hay demanda de transistores a nanoescala para circuitos digitales eficientes, y la polarización de cada dispositivo es fundamental. Estas estrictas condiciones de polarización se pueden relajar obteniendo valores precisos de los voltajes umbral del transistor. Esto conduce a estados lógicos más tolerantes al ruido eléctrico.

Para cumplir con los requisitos de consumo de energía reducido, los transistores de efecto de campo (FET) CMOS se fabrican de manera que funcionen en modo de mejora (E), es decir, no hay portadores de carga libres en el canal con voltaje de puerta cero. Por otro lado, los transistores en modo de agotamiento (D) tienen corrientes más altas que en el modo de mejora debido a la amplia densidad de portadores de carga.

A diferencia de las aplicaciones de conmutación de FET, para aplicaciones de alta frecuencia, el estado apagado de FET no es un requisito obligatorio. De hecho, la presencia de un canal con polarización de puerta cero es ventajosa para obtener una alta transconductancia a voltajes más bajos. Para los FET de Si, los modos de mejora o agotamiento se determinaron en el paso de fabricación del dopaje por implantación de iones. Sin embargo, implementar esta solución para la nueva generación de materiales delgados como semiconductores orgánicos y materiales 2D es un desafío.

Según una nueva investigación publicada en ACS Applied Electronic Materials , al elegir una función de trabajo particular para un metal de puerta, los voltajes de umbral de los FET tipo p se pueden cambiar de valores negativos a positivos, lo que supone un cambio selectivo entre el modo de operación de mejora y el modo de agotamiento.

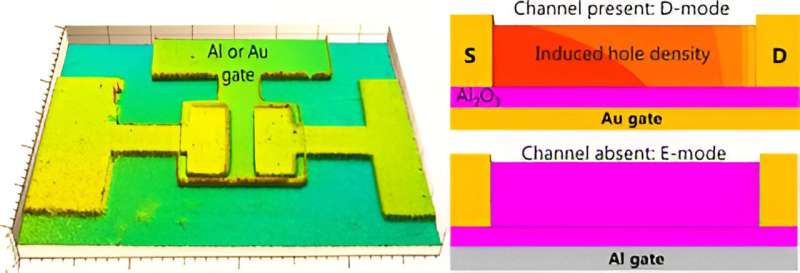

Los investigadores fabricaron experimentalmente los FET con varios electrodos metálicos de puerta que tenían diferentes funciones de trabajo. El espesor de la alúmina dieléctrica era de sólo 5 nm. Debido a esta corta separación entre el metal de la puerta y el canal semiconductor orgánico tipo p, hubo interacción electrostática entre ellos incluso sin la aplicación de voltaje externo. Cuando se utiliza un metal con función de bajo trabajo como el aluminio (4,4 eV), el FET funciona en modo de mejora.

Para metales de compuerta con función de alto trabajo como el oro (5,0 eV), se induce una cierta cantidad de agujeros en el canal con un voltaje de compuerta cero. Esto genera una buena cantidad de corriente, lo que se conoce como funcionamiento en modo de agotamiento.

Para confirmar esta observación experimental, los investigadores realizaron simulaciones de dispositivos TCAD. Las simulaciones produjeron gráficos de contornos de color de la densidad de agujeros inducidos. Este tipo de comparación de resultados experimentales y de simulación son muy importantes desde el punto de vista tecnológico y de producción a gran escala.

El autor principal, Dr. Abhay Sagade de SRMIST, India, reveló que los efectos observados son profundos para espesores dieléctricos delgados como los de menos de 10 nm. Para espesores mayores, los FET permanecen en modo de mejora incluso para metales de puerta con alta función de trabajo.

Este concepto puede extenderse fácilmente a cualquier material fino orgánico, inorgánico y 2D de nueva generación. Con este método, debería ser posible fabricar dispositivos y circuitos osciladores y lógicos digitales más compactos, precisos y reconfigurables. Además, los OFET en modo D con corrientes mejoradas se pueden utilizar de manera eficiente para aplicaciones de alta frecuencia.

Esto también tiene inmensas implicaciones para los próximos dispositivos cuánticos y aplicaciones tecnológicas que utilizan dispositivos sensibles a pequeñas dimensiones.

Más información: Abhay A. Sagade, Operación selectiva de modos de mejora y agotamiento de transistores de efecto de campo a nanoescala, Materiales electrónicos aplicados ACS (2024). DOI:10.1021/acsaelm.3c01825

Proporcionado por el Instituto de Ciencia y Tecnología SRM