Crédito:EPFL 2011

(PhysOrg.com) - Es posible que pronto sea posible fabricar las estructuras minúsculas que componen los transistores y los chips de silicio de forma rápida y económica. Los científicos suizos están investigando actualmente el uso de la litografía de estarcido dinámico, un método reciente pero aún no perfeccionado, para la creación de nanoestructuras.

Más rápido, menos costoso, y mejor. Estas son las ventajas de la litografía de plantilla dinámica, una nueva forma de fabricar nanoestructuras, como las diminutas estructuras de los transistores y los chips de silicio.

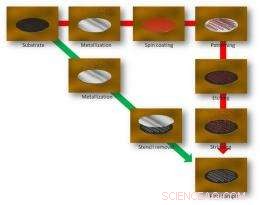

El principio de la técnica del "estarcido" para hacer estructuras a escala nanométrica (una millonésima de milímetro) es simple:se coloca un sustrato, una oblea de silicio (Si) o plásticos flexibles, en un evaporador. Encima hay una plantilla con aberturas, llamadas aperturas, aproximadamente 100-200 nanómetros de tamaño. Durante la evaporación del metal, la plantilla actúa como una máscara, y solo el metal que pasa por las aberturas aterriza sobre el sustrato. Por tanto, es posible depositar localmente metal sobre el sustrato en un patrón muy específico. Esta precisión es esencial para que los transistores u otros componentes electrónicos compuestos por estas estructuras funcionen correctamente. "Toma un trozo de papel, corta un círculo en el medio. Pon el resto del papel contra la pared, rocíe todo con pintura, y luego retire la plantilla. Tienes un lindo círculo. Este es esencialmente el principio que usamos, ”Dice Veronica Savu, que trabaja en el Laboratorio de Microsistemas de EPFL, dirigido por el profesor Juergen Brugger. "Usar plantillas para hacer algo no es nuevo, Ella continúa. Pero poder hacerlo a una escala tan pequeña es un verdadero desafío científico ".

Y Savu ya ha aceptado el desafío. Su investigación fue destacada en la portada de la revista científica Nanoescala este verano. También ha ganado recientemente una subvención de la Fundación Nacional de Ciencias de Suiza para continuar con su trabajo. Ella no está satisfecha con la litografía que usa una plantilla estática, como se describió anteriormente, porque impone varias limitaciones; obtener diferentes patrones de una sola plantilla es imposible, por ejemplo. Está interesada en la litografía de estarcido dinámico (DSL), un proceso novedoso que permite diseños personalizados utilizando la misma plantilla.

"Con una sola apertura, nuestra plantilla se puede mover durante la evaporación del metal, y puede dibujar varios patrones bidimensionales diferentes en una sola operación, como un cuadrado, un circulo, una línea o una cruz. Es como escribir un texto con un lápiz ”Ella explica. “También hemos demostrado que es posible utilizar este método en un sustrato de 100 mm de diámetro, el tamaño estándar utilizado en la industria ”. Hasta este punto, nadie ha logrado hacer todo lo necesario para aplicar DSL a nanoescala en el mundo real. "Sabíamos sobre DSL, sobre aberturas de plantilla de tamaño submicrométrico, y sobre el uso de plantillas en muestras de silicio de tamaño industrial. Pero nadie había podido aun reunir todos esos elementos en un solo método ".

Por lo tanto, la litografía de esténcil estática o dinámica podría eventualmente usarse en la industria, reemplazando los métodos tradicionales de nanolitografía llamados "basados en resistencias". Esos son procesos complicados y costosos. “El uso de esténciles en modo estático representa una democratización de la nanolitografía, sin necesidad de maquinaria costosa, solo una plantilla y un evaporador, ”Dice el profesor Brugger.

"Ahora, Vamos a colaborar con el Centro de Nanociencia de la Universidad de Basilea para realizar las pruebas necesarias para demostrar una aplicación real de la litografía de estarcido dinámico, ”, Explica Veronica Savu. "El objetivo es eventualmente hacer transistores funcionales, posiblemente usando grafeno o nanocables, como ya hemos hecho con la litografía de estarcido estático ".