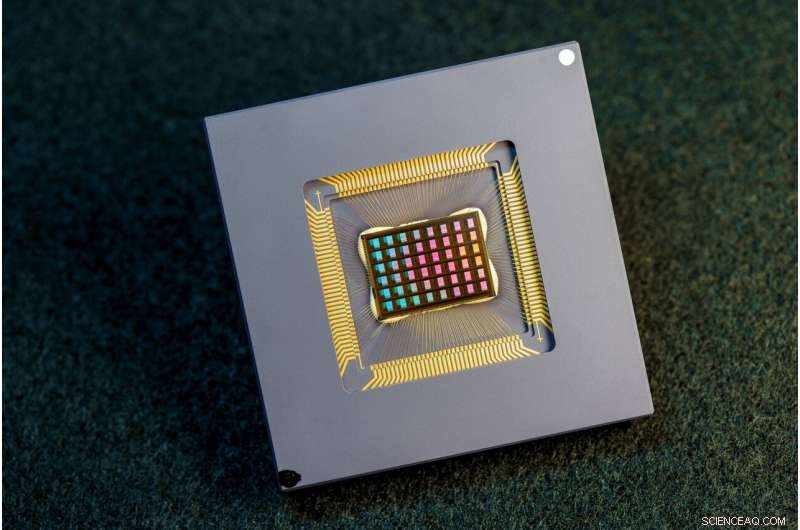

Un equipo de investigadores internacionales diseñó, fabricó y probó el chip NeuRRAM. Crédito:David Baillot/Universidad de California en San Diego

Un equipo internacional de investigadores ha diseñado y construido un chip que ejecuta cálculos directamente en la memoria y puede ejecutar una amplia variedad de aplicaciones de IA, todo con una fracción de la energía que consumen las plataformas informáticas para la informática de IA de propósito general.

El chip neuromórfico NeuRRAM lleva a la IA un paso más cerca de ejecutarse en una amplia gama de dispositivos de borde, desconectados de la nube, donde pueden realizar tareas cognitivas sofisticadas en cualquier lugar y en cualquier momento sin depender de una conexión de red a un servidor centralizado. Las aplicaciones abundan en todos los rincones del mundo y en todas las facetas de nuestras vidas, y van desde relojes inteligentes hasta auriculares VR, auriculares inteligentes, sensores inteligentes en fábricas y rovers para la exploración espacial.

El chip NeuRRAM no solo tiene el doble de eficiencia energética que los chips de "cómputo en memoria" de última generación, una clase innovadora de chips híbridos que ejecutan cálculos en la memoria, sino que también brinda resultados que son tan precisos como chips digitales convencionales. Las plataformas de IA convencionales son mucho más voluminosas y, por lo general, están restringidas al uso de grandes servidores de datos que operan en la nube.

Además, el chip NeuRRAM es muy versátil y admite muchos modelos y arquitecturas de redes neuronales diferentes. Como resultado, el chip se puede utilizar para muchas aplicaciones diferentes, incluido el reconocimiento y la reconstrucción de imágenes, así como el reconocimiento de voz.

"La sabiduría convencional es que la mayor eficiencia de la computación en memoria es a costa de la versatilidad, pero nuestro chip NeuRRAM obtiene eficiencia sin sacrificar la versatilidad", dijo Weier Wan, el primer autor correspondiente del artículo y un Ph.D. reciente. graduado de la Universidad de Stanford que trabajó en el chip mientras estaba en UC San Diego, donde fue co-asesorado por Gert Cauwenberghs en el Departamento de Bioingeniería.

El equipo de investigación, codirigido por bioingenieros de la Universidad de California en San Diego, presenta sus resultados en la edición del 17 de agosto de Nature .

Actualmente, la computación de IA consume mucha energía y es costosa desde el punto de vista computacional. La mayoría de las aplicaciones de IA en dispositivos perimetrales implican mover datos de los dispositivos a la nube, donde la IA los procesa y analiza. Luego, los resultados se vuelven a mover al dispositivo. Esto se debe a que la mayoría de los dispositivos perimetrales funcionan con baterías y, como resultado, solo tienen una cantidad limitada de energía que se puede dedicar a la informática.

Al reducir el consumo de energía necesario para la inferencia de IA en el borde, este chip NeuRRAM podría generar dispositivos de borde más robustos, inteligentes y accesibles y una fabricación más inteligente. También podría conducir a una mejor privacidad de los datos, ya que la transferencia de datos de los dispositivos a la nube conlleva mayores riesgos de seguridad.

En los chips de IA, mover datos de la memoria a las unidades informáticas es un cuello de botella importante.

"Es el equivalente a hacer un viaje de ocho horas por un día laboral de dos horas", dijo Wan.

Para resolver este problema de transferencia de datos, los investigadores utilizaron lo que se conoce como memoria resistiva de acceso aleatorio, un tipo de memoria no volátil que permite el cálculo directamente dentro de la memoria en lugar de unidades informáticas separadas. RRAM y otras tecnologías de memoria emergentes utilizadas como conjuntos de sinapsis para computación neuromórfica fueron pioneros en el laboratorio de Philip Wong, asesor de Wan en Stanford y uno de los principales contribuyentes de este trabajo. La computación con chips RRAM no es necesariamente nueva, pero generalmente conduce a una disminución en la precisión de los cálculos realizados en el chip y una falta de flexibilidad en la arquitectura del chip.

"La computación en memoria ha sido una práctica común en la ingeniería neuromórfica desde que se introdujo hace más de 30 años", dijo Cauwenberghs. "Lo que es nuevo con NeuRRAM es que la eficiencia extrema ahora va de la mano con una gran flexibilidad para diversas aplicaciones de IA casi sin pérdida de precisión en comparación con las plataformas de cómputo de uso general digital estándar".

Una metodología cuidadosamente elaborada fue clave para el trabajo con múltiples niveles de "cooptimización" en las capas de abstracción de hardware y software, desde el diseño del chip hasta su configuración para ejecutar varias tareas de IA. Además, el equipo se aseguró de tener en cuenta varias limitaciones que van desde la física del dispositivo de memoria hasta los circuitos y la arquitectura de la red.

"Este chip ahora nos brinda una plataforma para abordar estos problemas en toda la pila, desde dispositivos y circuitos hasta algoritmos", dijo Siddharth Joshi, profesor asistente de ciencias de la computación e ingeniería en la Universidad de Notre Dame, quien comenzó a trabajar en el proyecto como un doctorado estudiante e investigadora postdoctoral en el laboratorio de Cauwenberghs en UC San Diego.

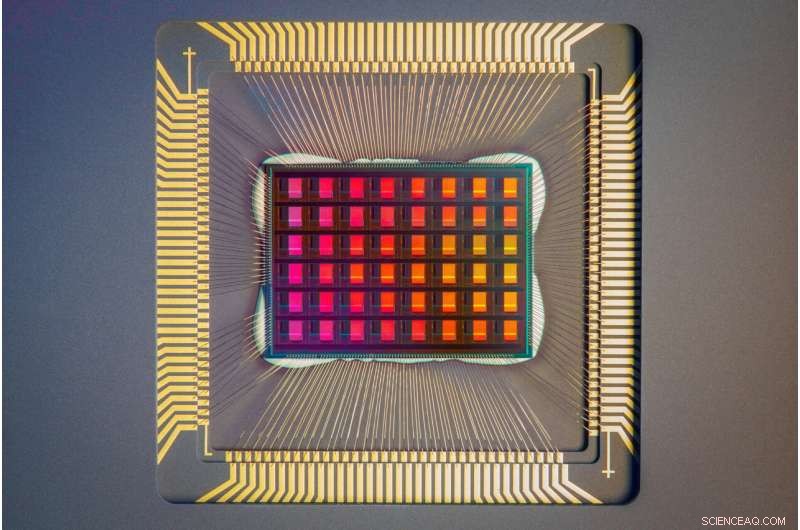

Un primer plano del chip NeuRRAM. Crédito:David Baillot/Universidad de California en San Diego

Rendimiento de chips

Los investigadores midieron la eficiencia energética del chip mediante una medida conocida como producto de retardo de energía o EDP. EDP combina tanto la cantidad de energía consumida para cada operación como la cantidad de tiempo que lleva completar la operación. Según esta medida, el chip NeuRRAM logra un EDP de 1,6 a 2,3 veces menor (cuanto más bajo, mejor) y una densidad computacional de 7 a 13 veces mayor que los chips de última generación.

Los investigadores ejecutaron varias tareas de IA en el chip. Logró una precisión del 99 % en una tarea de reconocimiento de dígitos escritos a mano; el 85,7% en una tarea de clasificación de imágenes; y el 84,7 % en una tarea de reconocimiento de comandos de voz de Google. Además, el chip también logró una reducción del 70 % en el error de reconstrucción de imágenes en una tarea de recuperación de imágenes. Estos resultados son comparables a los chips digitales existentes que realizan cálculos con la misma precisión de bits, pero con ahorros drásticos de energía.

Researchers point out that one key contribution of the paper is that all the results featured are obtained directly on the hardware. In many previous works of compute-in-memory chips, AI benchmark results were often obtained partially by software simulation.

Next steps include improving architectures and circuits and scaling the design to more advanced technology nodes. Researchers also plan to tackle other applications, such as spiking neural networks.

"We can do better at the device level, improve circuit design to implement additional features and address diverse applications with our dynamic NeuRRAM platform," said Rajkumar Kubendran, an assistant professor for the University of Pittsburgh, who started work on the project while a Ph.D. student in Cauwenberghs' research group at UC San Diego.

In addition, Wan is a founding member of a startup that works on productizing the compute-in-memory technology. "As a researcher and an engineer, my ambition is to bring research innovations from labs into practical use," Wan said.

New architecture

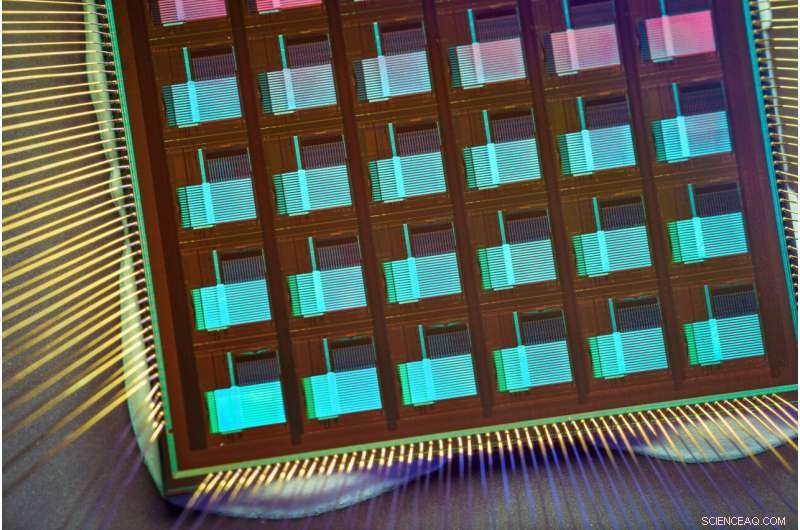

The key to NeuRRAM's energy efficiency is an innovative method to sense output in memory. Conventional approaches use voltage as input and measure current as the result. But this leads to the need for more complex and more power hungry circuits. In NeuRRAM, the team engineered a neuron circuit that senses voltage and performs analog-to-digital conversion in an energy efficient manner. This voltage-mode sensing can activate all the rows and all the columns of an RRAM array in a single computing cycle, allowing higher parallelism.

In the NeuRRAM architecture, CMOS neuron circuits are physically interleaved with RRAM weights. It differs from conventional designs where CMOS circuits are typically on the peripheral of RRAM weights.The neuron's connections with the RRAM array can be configured to serve as either input or output of the neuron. This allows neural network inference in various data flow directions without incurring overheads in area or power consumption. This in turn makes the architecture easier to reconfigure.

To make sure that accuracy of the AI computations can be preserved across various neural network architectures, researchers developed a set of hardware algorithm co-optimization techniques. The techniques were verified on various neural networks including convolutional neural networks, long short-term memory, and restricted Boltzmann machines.

As a neuromorphic AI chip, NeuroRRAM performs parallel distributed processing across 48 neurosynaptic cores. To simultaneously achieve high versatility and high efficiency, NeuRRAM supports data-parallelism by mapping a layer in the neural network model onto multiple cores for parallel inference on multiple data. Also, NeuRRAM offers model-parallelism by mapping different layers of a model onto different cores and performing inference in a pipelined fashion.

The NeuRRAM chip uses an innovative architecture that has been co-optimized across the stack. Credit:David Baillot/University of California San Diego

An international research team

The work is the result of an international team of researchers.

The UC San Diego team designed the CMOS circuits that implement the neural functions interfacing with the RRAM arrays to support the synaptic functions in the chip's architecture, for high efficiency and versatility. Wan, working closely with the entire team, implemented the design; characterized the chip; trained the AI models; and executed the experiments. Wan also developed a software toolchain that maps AI applications onto the chip.

The RRAM synapse array and its operating conditions were extensively characterized and optimized at Stanford University.

The RRAM array was fabricated and integrated onto CMOS at Tsinghua University.

The Team at Notre Dame contributed to both the design and architecture of the chip and the subsequent machine learning model design and training. A four-megabit nvCIM macro for edge AI devices