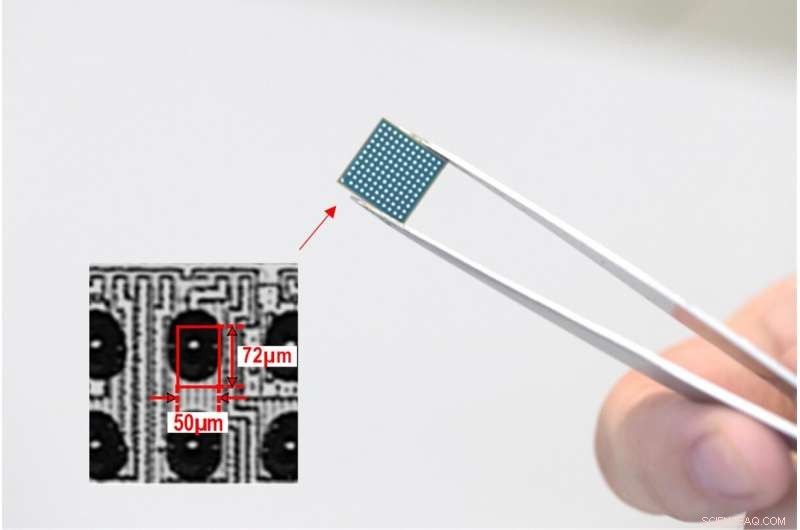

Todo el PLL totalmente digital encaja en una región de 50 × 72 μm2, lo que lo convierte en el PLL más pequeño hasta la fecha. Crédito:Kenichi Okada

Los científicos del Instituto de Tecnología de Tokio (Tokyo Tech) y Socionext Inc. han diseñado el bucle de bloqueo de fase (PLL) totalmente digital más pequeño del mundo. Los PLL son circuitos de reloj críticos en prácticamente todas las aplicaciones digitales, y reducir su tamaño y mejorar su desempeño es un paso necesario para permitir el desarrollo de tecnologías de próxima generación.

Tecnologías nuevas o mejoradas, como la inteligencia artificial, Comunicaciones celulares 5G, e Internet de las cosas, se espera que traigan cambios revolucionarios en la sociedad. Pero para que eso suceda, Los dispositivos de sistema en un chip (SoC) de alto rendimiento, un tipo de circuito integrado, son indispensables. Un componente básico de los dispositivos SoC es el bucle de bloqueo de fase (PLL), un circuito que se sincroniza con la frecuencia de una oscilación de referencia y emite una señal con la misma o mayor frecuencia. Los PLL generan 'señales de reloj, 'cuyas oscilaciones actúan como un metrónomo que proporciona una referencia de tiempo precisa para el funcionamiento armonioso de los dispositivos digitales.

Para que se realicen dispositivos SoC de alto rendimiento, Los procesos de fabricación de la electrónica de semiconductores deben volverse más sofisticados. Cuanto menor sea el área para implementar circuitos digitales, mejor será el rendimiento del dispositivo. Los fabricantes se han apresurado a desarrollar semiconductores cada vez más pequeños. Los semiconductores de 7 nm (una mejora masiva con respecto a su predecesor de 10 nm) ya están en producción, y ahora se están estudiando métodos para construir unos de 5 nm.

Sin embargo, en este empeño se encuentra un cuello de botella importante. Los PLL existentes requieren componentes analógicos, que generalmente son voluminosos y tienen diseños que son difíciles de reducir.

Científicos de Tokyo Tech y Socionext Inc., dirigido por el profesor Kenichi Okada, han abordado este problema mediante la implementación de un PLL fraccional-N 'sintetizable, que solo requiere puertas lógicas digitales, y sin componentes analógicos voluminosos, lo que facilita su adopción en circuitos integrados miniaturizados convencionales.

Okada y su equipo utilizaron varias técnicas para reducir el área requerida, consumo de energía y jitter (fluctuaciones de tiempo no deseadas al transmitir señales digitales) de sus PLL sintetizables. Para disminuir el área, emplearon un oscilador de anillo, un oscilador compacto que se puede reducir fácilmente. Para suprimir el jitter, redujeron el ruido de fase (fluctuaciones aleatorias en una señal) de este oscilador de anillo, utilizando "bloqueo de inyección", el proceso de sincronizar un oscilador con una señal externa cuya frecuencia (o un múltiplo de ella) es cercana a la del oscilador, en un amplio rango de frecuencias. El ruido de fase más bajo, Sucesivamente, consumo de energía reducido.

El diseño de este PLL sintetizable supera al de todos los demás PLL de última generación en muchos aspectos importantes. Logra el mejor rendimiento de fluctuación con el menor consumo de energía y el área más pequeña (como se puede ver en la Figura 1). "El área del núcleo es 0,0036 mm2, y todo el PLL se implementa como un diseño con una sola fuente de alimentación, "comenta Okada. Además, se puede construir utilizando herramientas de diseño digital estándar, teniendo en cuenta su rapidez, poco esfuerzo y producción de bajo costo, haciéndolo comercialmente viable.

Este PLL sintetizable se puede integrar fácilmente en el diseño de SoC totalmente digitales, y es comercialmente viable, haciéndolo valioso para desarrollar el muy buscado semiconductor de 5 nm para aplicaciones de vanguardia, incluida la inteligencia artificial, internet de las cosas y muchos otros, donde el alto rendimiento y el bajo consumo de energía serían los requisitos críticos. Pero los aportes de esta investigación van más allá de estas posibilidades. "Nuestro trabajo demuestra el potencial de los circuitos sintetizables. Con la metodología de diseño empleada aquí, otros componentes básicos de los SoC, como convertidores de datos, circuitos de administración de energía, y transceptores inalámbricos, también podría hacerse sintetizable. Esto aumentaría enormemente la productividad del diseño y reduciría considerablemente los esfuerzos de diseño, "explica Okada. Tokyo Tech y Socionext continuarán su colaboración en este campo para avanzar en la miniaturización de dispositivos electrónicos, permitiendo la realización de tecnologías de nueva generación.