La arquitectura general de un MOSFET tradicional frente a un FET 2D. Un FET (transistor de efecto de campo) es un dispositivo para regular el flujo de portadores de carga (como electrones) a través de un canal con tres terminales:una fuente, un drenaje y una puerta. Un MOSFET (transistor de efecto de campo semiconductor de óxido de metal) es, con mucho, el tipo de FET más utilizado y es un componente básico de la electrónica moderna, utilizado en dispositivos electrónicos comerciales durante más de 50 años. Una diferencia principal entre el MOSFET 3D tradicional y la "tecnología emergente" del FET 2D es que el canal en un MOSFET tradicional está en un material 3D, mientras que el canal de un FET 2D es un material 2D. Crédito:Sean Kelley/NIST

Los transistores son los componentes básicos de la electrónica moderna y se utilizan en todo, desde televisores hasta computadoras portátiles. A medida que los transistores se han vuelto más pequeños y compactos, también lo ha hecho la electrónica, razón por la cual su teléfono celular es una computadora súper poderosa que cabe en la palma de su mano.

Pero hay un problema de escala:los transistores ahora son tan pequeños que son difíciles de apagar. Un elemento clave del dispositivo es el canal por el que viajan los portadores de carga (como los electrones) entre los electrodos. Si ese canal se acorta demasiado, los efectos cuánticos permiten que los electrones salten de un lado a otro, incluso cuando no deberían hacerlo.

Una forma de superar este obstáculo de tamaño es usar capas de materiales 2D, que tienen solo un átomo de espesor, como canal. Los canales atómicamente delgados pueden ayudar a habilitar transistores aún más pequeños al dificultar que los electrones salten entre los electrodos. Un ejemplo bien conocido de un material 2D es el grafeno, cuyos descubridores ganaron el Premio Nobel de Física en 2010. Pero hay otros materiales 2D, y muchos creen que son el futuro de los transistores, con la promesa de reducir el grosor del canal desde su límite 3D actual de unos pocos nanómetros (nm, mil millonésimas de metro) a menos de un solo nanómetro de espesor.

Aunque la investigación se ha disparado en esta área, un problema se ha pasado por alto persistentemente, según un equipo de científicos del Instituto Nacional de Estándares y Tecnología (NIST), la Universidad de Purdue, la Universidad de Duke y la Universidad Estatal de Carolina del Norte. Los materiales 2D y sus interfaces, que los investigadores pretenden que sean planos cuando se apilan unos encima de otros, pueden, de hecho, no ser planos. Esta falta de planitud, a su vez, puede afectar significativamente el rendimiento del dispositivo, a veces para bien y otras para mal.

En un nuevo estudio publicado en la edición del 26 de abril de 2022 de ACS Nano , el equipo de investigación informa los resultados de sus mediciones de la planitud de estas interfaces en dispositivos de transistores que incorporan materiales 2D. Son el primer grupo en tomar imágenes de microscopía de alta resolución que muestran la planitud de estas capas 2D en conjuntos de dispositivos completos, en una escala relativamente grande, alrededor de 12 micrómetros (millonésimas de metro) en comparación con los 10 nm a 100 nm más comunes. rango nm.

Los científicos obtuvieron imágenes con éxito de una serie de interfaces 2D-2D y 2D-3D en dispositivos que crearon utilizando una variedad de métodos de fabricación comunes. Sus resultados muestran que suponer que las interfaces son planas cuando no lo son es un problema mucho mayor de lo que los investigadores en el campo podrían haberse dado cuenta.

"Estamos informando a la comunidad sobre un problema que se ha pasado por alto", dijo Curt Richter del NIST. "Está retrasando la adopción de nuevos materiales. El primer paso para resolver el problema es saber que tienes un problema".

Los beneficios potenciales incluyen dar a la comunidad científica más control sobre la fabricación de sus dispositivos.

"La falta de comprensión sobre la planitud de la interfaz 2D es un obstáculo importante para mejorar los dispositivos basados en materiales 2D", dijo el autor principal Zhihui Cheng, del NIST y la Universidad de Purdue en el momento de la publicación. "Hemos presentado un método para cuantificar la planitud a la resolución de angstrom. Esto abre muchas ventanas para que las personas exploren la tensión y las interacciones en las interfaces 2D".

No tan plano como crees

En un transistor tradicional, un electrodo de fuente 3D libera electrones a través de un canal 3D a un electrodo de drenaje 3D. En los transistores 2D, los electrones viajan a través de un material 2D. Las áreas donde estos diferentes materiales se encuentran se llaman interfaces.

La falta de uniformidad en estas interfaces puede causar problemas con el flujo de corriente en dispositivos que utilizan materiales 2D. Por ejemplo, si existe un contacto físico íntimo entre la fuente de metal y el canal 2D, también habrá un contacto eléctrico íntimo y la corriente fluirá sin problemas. Por el contrario, los espacios entre el material del canal 2D y la fuente comprometen el contacto eléctrico, lo que reduce el flujo de corriente.

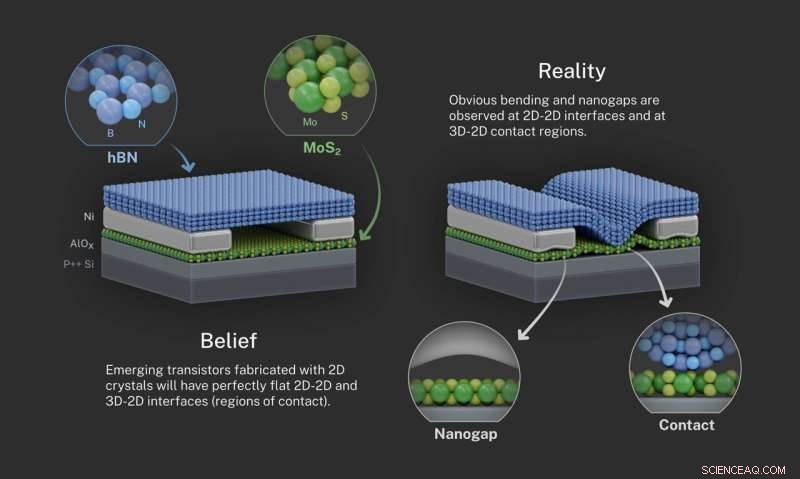

En su artículo, los investigadores exploran varios tipos diferentes de interfaces 2D, incluidas las creadas entre la fuente de níquel y los electrodos de drenaje, un canal 2D hecho del disulfuro de molibdeno cristalino 2D (MoS2 ), una capa de encapsulación del nitruro de boro hexagonal de cristal (hBN) y óxido de aluminio.

Los investigadores generalmente esperan que los transistores fabricados con cristales 2D tengan interfaces 2D-2D y 3D-2D perfectamente planas (regiones de contacto). Pero nueva evidencia muestra que, en realidad, hay flexión y nanoespacios obvios en estas interfaces. Crédito:Sean Kelley/NIST

Los científicos suelen colocar los materiales 2D y 3D uno encima del otro durante el proceso de fabricación del dispositivo. Por ejemplo, los investigadores a veces apilan materiales 2D en contactos metálicos prediseñados. Pero el equipo de investigación descubrió que este tipo de apilamiento de materiales 2D tenía un efecto profundo en su planitud, particularmente cerca de la región de contacto. Agregar hBN causó el MoS2 deformarse hasta 10 nm en un lado del contacto. Las áreas más alejadas de los contactos tendían a ser relativamente planas, aunque algunas de estas áreas todavía tenían un espacio de 2 a 3 nm.

Mientras probaba los efectos de la deposición de capas atómicas (una técnica común utilizada para depositar una capa delgada de material) en la planitud de la interfaz 2D, el equipo de investigación descubrió que una interfaz directa entre el óxido de aluminio y MoS2 está más deformado que las interfaces entre hBN y MoS2 . Al investigar la planitud de la interfaz de contacto 3D-2D, el equipo descubrió que se formaban nanocavidades sorprendentemente grandes en la interfaz entre los contactos de níquel y el MoS2 2D. canal.

Para conectar estas interfaces no planas con las preocupaciones del mundo real sobre el rendimiento del dispositivo, el equipo probó las características eléctricas de un transistor fabricado con estos materiales. Los investigadores descubrieron que la falta de planitud adicional en el canal tuvo el efecto de mejorar el rendimiento del dispositivo.

"En general, estos resultados revelan cuánto depende la estructura de las interfaces 2D-2D y 2D-3D de los materiales y del proceso de fabricación", dijo Cheng.

Para realizar sus observaciones, el grupo utilizó un tipo de microscopía electrónica de transmisión de barrido de alta resolución (TEM de barrido), capaz de resolver las imágenes al nivel de átomos individuales.

"Gran parte de este campo es pura investigación", dijo Richter. "La gente fabricará un dispositivo o tal vez dos, y no tienen extras que puedan darle a un microscopista para que los desmonte". En este estudio, por otro lado, el punto principal era hacer los dispositivos y luego analizarlos.

"No hicimos nada súper especial con las medidas", continuó Richter. "Pero la combinación de los conocimientos de medición eléctrica y la experiencia en TEM de alta resolución, eso no es algo común".

"Con la resolución sub-angstrom y la longitud de registro en TEM transversal, además de la correlación con las características del dispositivo, nuestro trabajo ha ampliado y profundizado los puntos de vista sobre la complejidad y la complejidad de las interfaces 2D", dijo Cheng.

Con beneficios para todos

Las aplicaciones del trabajo incluyen la reducción de la variación involuntaria de dispositivo a dispositivo, de la cual la planitud 2D es un factor contribuyente significativo, dijeron los investigadores.

El método de obtención de imágenes también podría, en última instancia, ayudar a los científicos a tener más control sobre la fabricación. Ciertos procesos introducen tensión mecánica en las estructuras 2D, retorciéndolas como una toallita escurrida o estrujándolas y estirándolas como un acordeón. Esto puede cambiar el rendimiento de un dispositivo de formas impredecibles que los científicos aún no comprenden del todo. Una mejor comprensión de cómo la tensión afecta el rendimiento del dispositivo puede dar a los investigadores un mayor control sobre este rendimiento.

"La tensión no siempre es algo malo", dijo Richter. "Los transistores de gama alta que la gente fabrica hoy en día en realidad tienen tensión incorporada para que funcionen mejor. Con los materiales 2D no es tan obvio cómo hacerlo, pero es posible usar la falta de planitud para crear la tensión que desea ."

Los autores esperan que su trabajo inspire nuevos esfuerzos para aumentar la resolución de las mediciones de planitud para interfaces 2D, incluso a una resolución de subangstrom.

"Tenemos algunos datos preliminares, pero en realidad es solo el comienzo de esta investigación", dijo Cheng. Las obleas MoS2 multicapa epitaxial prometen transistores de alto rendimiento