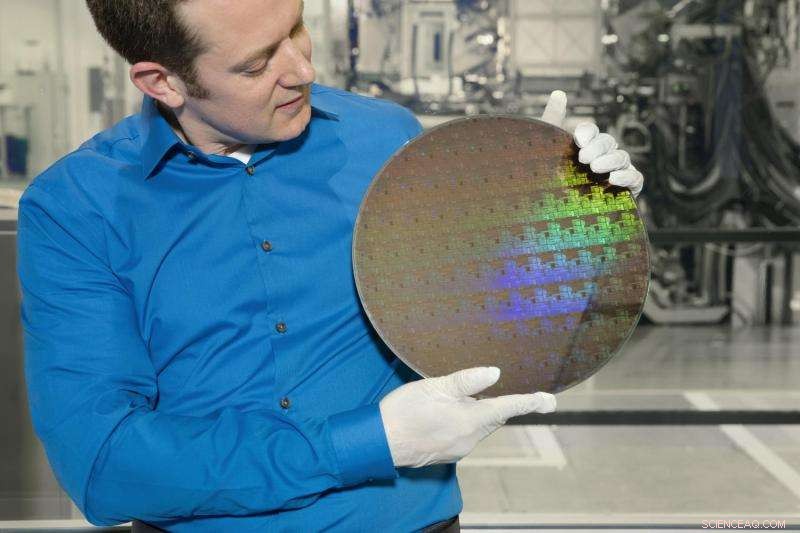

El científico de IBM Research, Nicolas Loubet, sostiene una oblea de chips con transistores de nanohojas de silicio de 5 nm fabricados mediante un proceso pionero en la industria que puede ofrecer una mejora del rendimiento del 40 por ciento a potencia fija. o un ahorro de energía del 75 por ciento con un rendimiento equivalente. Crédito:Connie Zhou

IBM, sus socios de Research Alliance Globalfoundries y Samsung, y los proveedores de equipos han desarrollado un proceso pionero en la industria para construir transistores de nanohojas de silicio que permitirán chips de 5 nanómetros (nm). Los detalles del proceso se presentarán en el simposio de 2017 sobre tecnología y circuitos VLSI en Kioto, Japón. En menos de dos años desde que se desarrolló un chip de nodo de prueba de 7 nm con 20 mil millones de transistores, Los científicos han allanado el camino para 30 mil millones de interruptores en un chip del tamaño de una uña.

El aumento resultante en el rendimiento ayudará a acelerar la computación cognitiva, Internet de las cosas (IoT), y otras aplicaciones de uso intensivo de datos entregadas en la nube. El ahorro de energía también podría significar que las baterías de los teléfonos inteligentes y otros productos móviles podrían durar de dos a tres veces más que los dispositivos actuales. antes de tener que cargarlo.

Científicos que trabajan como parte de la Alianza de Investigación dirigida por IBM en el Complejo NanoTech de las Facultades de Ciencias e Ingeniería a Nanoescala del Instituto Politécnico SUNY en Albany, NY logró el gran avance mediante el uso de pilas de nanohojas de silicio como la estructura del dispositivo del transistor, en lugar de la arquitectura estándar de FinFET, que es el modelo para la industria de los semiconductores hasta la tecnología de nodo de 7 nm.

"Para que las empresas y la sociedad satisfagan las demandas de la computación cognitiva y en la nube en los próximos años, el avance en la tecnología de semiconductores es esencial, "dijo Arvind Krishna, vicepresidente senior, Nube híbrida, y director, IBM Research. "Es por eso que IBM persigue agresivamente arquitecturas y materiales nuevos y diferentes que superen los límites de esta industria, y los lleva al mercado en tecnologías como mainframes y nuestros sistemas cognitivos ".

Científicos de IBM en el Complejo NanoTech de las Facultades de Ciencias e Ingeniería a Nanoescala del Instituto Politécnico SUNY en Albany, NY prepara obleas de prueba con transistores de nanohojas de silicio de 5 nm, cargado en la vaina unificada de apertura frontal, o FOUP, para probar un proceso pionero en la industria de construcción de transistores de 5 nm utilizando nanohojas de silicio. Crédito:Connie Zhou

La demostración del transistor de nanohojas de silicio, como se detalla en el documento de Research Alliance Transistor de puerta completa apilada de nanohojas para permitir el escalado más allá de FinFET, y publicado por VLSI, demuestra que los chips de 5 nm son posibles, mas poderoso, y no muy lejos en el futuro.

En comparación con la tecnología de vanguardia de 10 nm disponible en el mercado, una tecnología de 5 nm basada en nanohojas puede ofrecer una mejora del rendimiento del 40 por ciento a potencia fija, o un ahorro de energía del 75 por ciento con un rendimiento equivalente. Esta mejora permite un impulso significativo para satisfacer las demandas futuras de los sistemas de inteligencia artificial (IA), realidad virtual y dispositivos móviles.

Construyendo un nuevo interruptor

"Este anuncio es el último ejemplo de la investigación de clase mundial que sigue surgiendo de nuestra innovadora asociación público-privada en Nueva York, "dijo Gary Patton, CTO y Jefe de I + D mundial en Globalfoundries. "A medida que avanzamos hacia la comercialización de 7 nm en 2018 en nuestra planta de fabricación Fab 8, buscamos activamente tecnologías de próxima generación a 5 nm y más para mantener el liderazgo tecnológico y permitir a nuestros clientes producir un más rápido, y generación de semiconductores más rentable ".

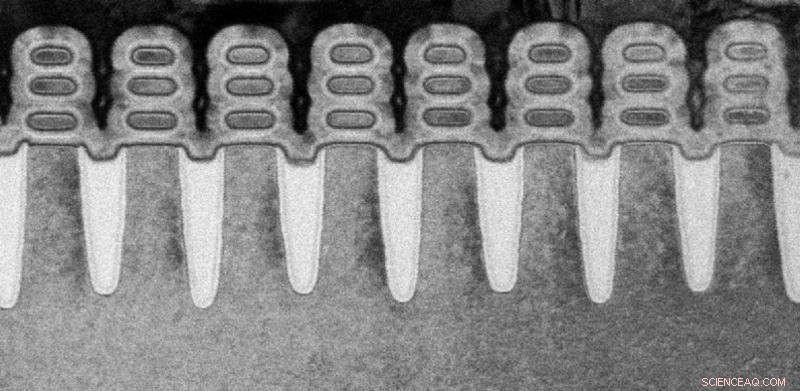

En la imagen:un escaneo del transistor de 5 nm de IBM Research Alliance, construido utilizando un proceso pionero en la industria para apilar nanohojas de silicio como la estructura del dispositivo, logrando una escala de 30 mil millones de conmutadores en un chip del tamaño de una uña que ofrecerá mejoras significativas de potencia y rendimiento sobre los chips de 10 nm de última generación. Crédito:IBM

IBM Research ha explorado la tecnología de semiconductores de nanohojas durante más de 10 años. Este trabajo es el primero en la industria en demostrar la viabilidad de diseñar y fabricar dispositivos de nanohojas apiladas con propiedades eléctricas superiores a la arquitectura FinFET.

Este mismo enfoque de litografía Ultravioleta Extrema (EUV) utilizado para producir el nodo de prueba de 7 nm y sus 20 mil millones de transistores se aplicó a la arquitectura de transistores de nanohojas. Usando litografía EUV, el ancho de las nanohojas se puede ajustar de forma continua, todo dentro de un único proceso de fabricación o diseño de chip. Esta capacidad de ajuste permite el ajuste fino del rendimiento y la potencia para circuitos específicos, algo que no es posible con la producción actual de arquitectura de transistores FinFET. que está limitado por la altura de su aleta portadora de corriente. Por lo tanto, mientras que los chips FinFET pueden escalar a 5 nm, simplemente reducir la cantidad de espacio entre las aletas no proporciona un mayor flujo de corriente para un rendimiento adicional.

"El anuncio de hoy continúa la colaboración del modelo público-privado con IBM que está energizando a SUNY-Polytechnic, Albany, y el liderazgo y la innovación del estado de Nueva York en el desarrollo de tecnologías de próxima generación, "dijo el Dr. Bahgat Sammakia, Presidente interino, Instituto Politécnico SUNY. "Creemos que habilitar el primer transistor de 5 nm es un hito importante para toda la industria de semiconductores a medida que continuamos avanzando más allá de las limitaciones de nuestras capacidades actuales. La asociación de SUNY Poly con IBM y Empire State Development es un ejemplo perfecto de cómo la industria, El gobierno y la academia pueden colaborar con éxito y tener un impacto amplio y positivo en la sociedad ".

Parte de los $ 3 mil millones de IBM, Inversión de cinco años en I + D de chips (anunciada en 2014), la prueba del escalado de la arquitectura de nanohojas a un nodo de 5 nm continúa el legado de contribuciones históricas de IBM a la innovación en silicio y semiconductores. Incluyen la invención o primera implementación de la DRAM de celda única, las leyes de escala de Dennard, fotorresistentes químicamente amplificados, cableado de interconexión de cobre, Silicio sobre aislante, ingeniería forzada, microprocesadores multinúcleo, litografía de inmersión, SiGe de alta velocidad, Dieléctricos de puerta alta k, DRAM incrustado, Aisladores de espacio de aire y apilamiento de chips 3-D.