La tensión mecánica de tracción puede tener un efecto útil para algunos transistores, donde la deformación atómica resultante permite a sus pares de agujeros de electrones portadores de corriente una mejor movilidad. Sin embargo, cuando ese estrés se aplica a todo el dispositivo, como es un enfoque popular mediante el uso de lo que se llama capas de parada de grabado por contacto (CESL), la región de deriva adyacente al canal estirado se comprime y da como resultado un rendimiento reducido.

Un equipo de investigación en China ha desarrollado un nuevo método CESL que introduce tensión de tracción tanto en el canal como en la región de deriva. mejorar el rendimiento general al ofrecer una baja resistencia a la deriva, alta frecuencia de corte y características de avería deseables. Su trabajo se describe en un artículo que aparece esta semana en la revista Anticipos de AIP .

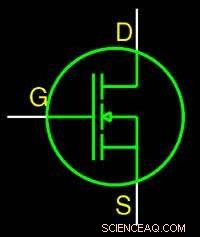

El equipo de investigadores se interesó en el método debido al trabajo realizado en técnicas de silicio deformado. Durante la investigación sobre transistores de efecto de campo semiconductor metaóxido tensado (MOSFET), Los investigadores vieron que la tensión en la región de origen / drenaje era inversa a la tensión de la región del canal. Con base en estas observaciones, comenzaron a estudiar cómo podrían utilizar este fenómeno de manera que pudiera mejorar el rendimiento.

Esta nueva investigación se centró en dispositivos de silicio sobre aislante parcial (PSOI) que introducen tensión de tracción tanto en el canal como en la región de deriva utilizando los CESL. Los resultados de la simulación también mostraron que el dispositivo PSOI ofrece un mejor rendimiento de frecuencia y capacidad de conducción que los dispositivos sin tensión.

"Lo más difícil para nosotros fue encontrar un bajo costo, Método compatible con CMOS para aplicar tensión mecánica, "dijo Xiangzhan Wang, de la Universidad de Ciencia y Tecnología Electrónica de China. "Durante el proceso de fabricación, la oblea se dobla a medida que crece la película de tensión (Si3N4), lo que crea un problema al mantener la oblea en el equipo de proceso ".

Los resultados del experimento, sin embargo, Mayor confianza en que la nueva técnica de deformación no solo podría aplicarse a dispositivos pequeños, sino también a dispositivos bastante grandes para mejorar el rendimiento. Con los resultados, incluso el equipo de investigación se sorprendió del nivel de mejora que aportó a sus simulaciones.

"En nuestra simulación, el LDMOSFET de tipo n PSOI totalmente tensado mostró una mejora de la corriente de conducción del 20-30 por ciento sobre el LDMOSFET de Si normal, "Dijo Wang." Pero cuando usamos este método de cepa con un producto comercial de Si LDMOS, la corriente de conducción se duplicó produciendo un aumento de corriente de más del 100 por ciento, lo cual fue bastante sorprendente para nosotros ".

Si bien este trabajo ha contribuido a la comprensión de los mecanismos de Si tensos, aún hay más por mejorar y comprender.

"Las siguientes direcciones de investigación para el equipo son optimizar el proceso de fabricación de estos dispositivos con el fin de obtener una mejor estabilidad e intentar aplicar el mismo método a un dispositivo asimétrico como un túnel FET, "Dijo Wang.