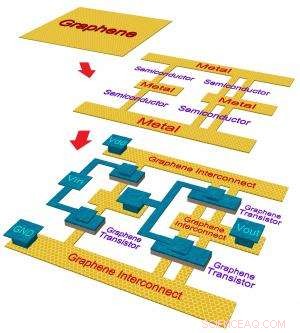

El esquema superior es una hoja de grafeno monocapa. El esquema central muestra cintas anchas / estrechas grabadas que actúan como semiconductores / metal. El esquema inferior es un circuito completamente de grafeno después de la deposición y el modelado del metal y el dieléctrico de la puerta. Crédito:Laboratorio de investigación de nanoelectrónica de UCSB

(Phys.org) —Investigadores en ingeniería eléctrica e informática de la Universidad de California, Santa Bárbara ha introducido y modelado un esquema de diseño de circuitos integrados en el que los transistores y las interconexiones se modelan de manera monolítica sin problemas en una hoja de grafeno. un plano bidimensional de átomos de carbono. La demostración ofrece posibilidades de ultraeficiencia energética, flexible, y electrónica transparente.

Los materiales a granel comúnmente utilizados para fabricar transitores e interconexiones CMOS plantean desafíos fundamentales en la reducción continua de sus tamaños de características y sufren de una creciente "resistencia de contacto" entre ellos. ambos conducen a una degradación del rendimiento y un aumento del consumo de energía. Los transistores e interconexiones basados en grafeno son una tecnología a nanoescala prometedora que podría abordar los problemas de los transistores tradicionales basados en silicio y las interconexiones metálicas.

"Además de sus superficies atómicamente delgadas y prístinas, el grafeno tiene una banda prohibida sintonizable, que se puede ajustar mediante el boceto litográfico de patrones; las cintas de grafeno estrechas se pueden hacer semiconductoras mientras que las cintas más anchas son metálicas. Por eso, Se pueden imaginar cintas de grafeno contiguas a partir del mismo material de partida para diseñar dispositivos tanto activos como pasivos de manera transparente y con menores resistencias de interfaz / contacto. "explicó Kaustav Banerjee, profesor de ingeniería eléctrica e informática y director del Laboratorio de Investigación de Nanoelectrónica de la UCSB. El equipo de investigación de Banerjee también incluye a los investigadores de UCSB Jiahao Kang, Deblina Sarkar y Yasin Khatami. Su trabajo fue publicado recientemente en la revista Letras de física aplicada .

"La evaluación precisa del transporte eléctrico a través de los diversos dispositivos e interconexiones basados en nanocintas de grafeno y a través de sus interfaces fue clave para nuestro exitoso diseño y optimización de circuitos, "explicó Jiahao Kang, estudiante de doctorado en el grupo de Banerjee y coautor del estudio. El grupo de Banerjee fue pionero en una metodología que utiliza la técnica de la función de verde sin equilibrio (NEGF) para evaluar el rendimiento de estos esquemas de circuitos complejos que involucran muchas heterouniones. Esta metodología se utilizó en el diseño de un circuito lógico "todo-grafeno" informado en este estudio.

"Este trabajo ha demostrado una solución para el grave problema de resistencia de contacto que se encuentra en la tecnología de semiconductores convencional al proporcionar una idea innovadora de utilizar un esquema de interconexión de dispositivos totalmente de grafeno. Esto simplificará significativamente el proceso de fabricación de circuitos integrados de dispositivos nanoelectrónicos basados en grafeno". comentó Philip Kim, profesor de física en la Universidad de Columbia, y un científico de renombre en el mundo del grafeno.

Como se informó en su estudio, Los circuitos de grafeno propuestos han logrado márgenes de ruido 1,7 veces más altos y 1-2 décadas menos de consumo de energía estática que la tecnología CMOS actual. Según Banerjee, con los esfuerzos mundiales en curso en el modelado y el dopaje del grafeno, estos circuitos se pueden realizar en un futuro próximo.

"Esperamos que este trabajo anime e inspire a otros investigadores a explorar el grafeno y los cristales bidimensionales emergentes más allá del grafeno para diseñar tales circuitos de ingeniería de banda prohibida" en un futuro próximo, "añadió Banerjee.