La fotónica ofrece varias ventajas, incluida la habilitación de comunicaciones de alta velocidad y bajas pérdidas al aprovechar las propiedades de la luz en los dominios de comunicación óptica de datos, aplicaciones biomédicas, tecnología automotriz y inteligencia artificial. Estas ventajas se obtienen a través de complejos circuitos fotónicos, que comprenden diversos elementos fotónicos que se integran en un chip fotónico.

Luego se añaden chips electrónicos para complementar los chips fotónicos para determinadas funciones, como el funcionamiento, la modulación y la amplificación de la fuente de luz. La estrecha integración de chips electrónicos y fotónicos en un sustrato es un aspecto crítico del embalaje fotónico.

El embalaje fotónico desempeña un papel vital a la hora de respaldar el funcionamiento eficaz de los chips electrónicos y fotónicos en los dominios eléctrico, óptico, mecánico y térmico. La gestión térmica eficiente se vuelve crucial en paquetes compactos donde la diafonía térmica entre chips electrónicos y fotónicos, junto con las fluctuaciones de la temperatura ambiente, pueden afectar negativamente el rendimiento de los chips fotónicos.

Los sustratos de vidrio, ampliamente discutidos como una plataforma de empaquetamiento conjunto para chips electrónicos y fotónicos, son fundamentales aquí porque ofrecen ventajas como un factor de forma compacto, baja pérdida eléctrica y una plataforma fabricable a nivel de panel. Además, los sustratos de vidrio tienen una baja conductividad térmica, lo que facilita una mínima propagación lateral del calor entre los chips electrónicos y fotónicos.

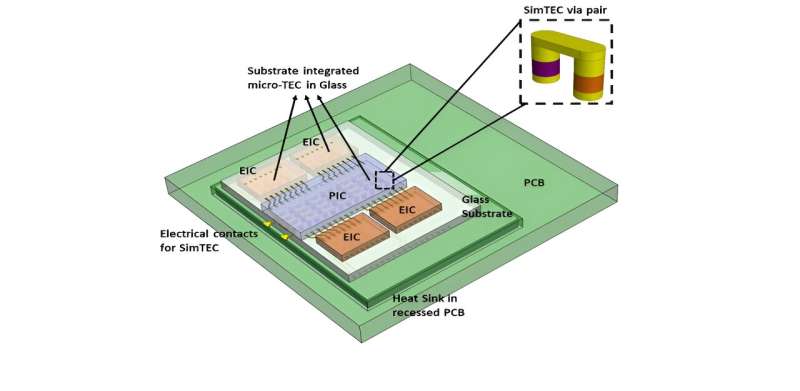

La incorporación de vías pasantes de vidrio (TGV) en el sustrato de vidrio permite una disipación eficaz del calor de los chips electrónicos. Otra estrategia de gestión térmica implica la integración de refrigeradores microtermoeléctricos (micro-TEC) en la parte inferior de un chip, lo que proporciona un control activo de la temperatura.

En una nueva investigación publicada en el Journal of Optical Microsystems , se presenta una combinación de tecnologías TGV y micro-TEC denominadas "refrigeradores microtermoeléctricos integrados en sustrato (SimTEC)".

SimTEC utiliza TGV parcialmente llenos de cobre y materiales termoeléctricos, lo que garantiza la estabilización térmica de los chips fotónicos y electrónicos del paquete. Esta novedosa técnica complementa los enfoques de enfriamiento a nivel de sistema. La investigadora Parnika Gupta y sus colegas del University College Cork (Irlanda) examinaron el impacto de los sustratos de vidrio en el rendimiento térmico de las vías segmentadas y lo compararon con el de los pilares micro-TEC independientes. Analizaron el efecto del diámetro, la altura, el paso y el factor de llenado de la vía en el rendimiento de refrigeración de SimTEC.

En particular, la tecnología proporciona un control térmico preciso en el paquete y reduce la resistencia térmica entre la superficie TEC y la interfaz del chip cuando los chips se unen mediante un chip invertido al sustrato de vidrio. Las simulaciones con diseño de experimentos (DOE) indican un enfriamiento máximo de 9,3 K o un rango de estabilización de temperatura de 18,6 K.

El estudio también destacó una variación seis veces mayor en el rendimiento de refrigeración con la variación en la geometría de la vía en comparación con la variación del rendimiento de refrigeración del unipar micro-TEC independiente. La optimización de las propiedades de los materiales termoeléctricos tiene el potencial de mejorar el rendimiento de futuras arquitecturas integradas en SimTEC.

Más información: Parnika Gupta et al, Refrigeradores microtermoeléctricos integrados en sustrato en sustrato de vidrio para paquetes fotónicos de próxima generación, Journal of Optical Microsystems (2024). DOI:10.1117/1.JOM.4.1.011006

Proporcionado por SPIE