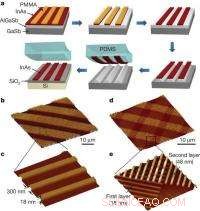

La fabricación de un dispositivo de óxido de indio (InAs) comienza con a) el crecimiento epitaxial y el grabado de InAs en matrices de nanocintas que se estampan sobre un sustrato de silicio / sílice (Si / SiO2); b) yc) matrices de nanocintas de InAs sobre Si / SiO2; d) ye) Superestructuras de nanocintas de InAs sobre Si / SiO2. Crédito:cortesía de Ali Javey, UC Berkeley

Hay buenas noticias en la búsqueda de la próxima generación de semiconductores. Investigadores del Laboratorio Nacional Lawrence Berkeley del Departamento de Energía de EE. UU. Y la Universidad de California Berkeley, han integrado con éxito capas ultrafinas del semiconductor arseniuro de indio en un sustrato de silicio para crear un transistor a nanoescala con excelentes propiedades electrónicas. Miembro de la familia de semiconductores III-V, El arseniuro de indio ofrece varias ventajas como alternativa al silicio, incluida la movilidad y velocidad superior de los electrones, lo que lo convierte en un candidato destacado para el futuro de bajo consumo, dispositivos electrónicos de alta velocidad.

"Hemos mostrado una ruta simple para la integración heterogénea de capas de arseniuro de indio hasta un espesor de 10 nanómetros en sustratos de silicio, "dice Ali Javey, un científico de la facultad en la División de Ciencias de Materiales de Berkeley Lab y un profesor de ingeniería eléctrica y ciencias de la computación en UC Berkeley, quien dirigió esta investigación.

"Se demostró que los dispositivos que fabricamos posteriormente operan cerca de los límites de rendimiento proyectados de los dispositivos III-V con una corriente de fuga mínima. Nuestros dispositivos también exhibieron un rendimiento superior en términos de densidad de corriente y transconductancia en comparación con los transistores de silicio de dimensiones similares".

A pesar de todas sus maravillosas propiedades electrónicas, El silicio tiene limitaciones que han provocado una intensa búsqueda de semiconductores alternativos para su uso en dispositivos futuros. Javey y su grupo de investigación se han centrado en semiconductores compuestos III-V, que presentan excelentes propiedades de transporte de electrones. El desafío ha sido encontrar una manera de conectar estos semiconductores compuestos en el bien establecido, tecnología de procesamiento de bajo costo utilizada para producir los dispositivos basados en silicio actuales. Dado el gran desajuste de celosía entre el silicio y los semiconductores compuestos III-V, El crecimiento heteroepitaxial directo de III-V en sustratos de silicio es desafiante y complejo, ya menudo resulta en un gran volumen de defectos.

"Hemos demostrado lo que llamamos un 'XOI, 'o plataforma tecnológica de semiconductores sobre aisladores compuestos, que es paralelo al SOI de hoy, 'o plataforma de silicona sobre aislante, "dice Javey." Usando un método de transferencia epitaxial, transferimos capas ultrafinas de arseniuro de indio monocristalino sobre sustratos de silicio / sílice, luego fabricó dispositivos utilizando técnicas de procesamiento convencionales para caracterizar el material XOI y las propiedades del dispositivo ".

Los resultados de esta investigación se han publicado en la revista Naturaleza, en un papel titulado, "Semiconductor compuesto ultradelgado en capas aislantes para transistores a nanoescala de alto rendimiento". Los coautores del informe con Javey fueron Hyunhyub Ko, Kuniharu Takei, Rehan Kapadia, Steven Chuang, Hui Fang, Paul Leu, Kartik Ganapathi, Elena Plis, Ha Sul Kim, Szu-Ying Chen, Morten Madsen, Alexandra Ford, Yu-Lun Chueh, Sanjay Krishna y Sayeef Salahuddin.

Para hacer sus plataformas XOI, Javey y sus colaboradores cultivaron películas delgadas de arseniuro de indio monocristalino (de 10 a 100 nanómetros de espesor) en un sustrato de fuente preliminar y luego modelaron litográficamente las películas en matrices ordenadas de nanocintas. Después de ser eliminado del sustrato de origen mediante un grabado en húmedo selectivo de una capa de sacrificio subyacente, las matrices de nanocintas se transfirieron al sustrato de silicio / sílice mediante un proceso de estampado.

Javey atribuyó el excelente rendimiento electrónico de los transistores XOI a las pequeñas dimensiones de la capa "X" activa y al papel fundamental que desempeña el confinamiento cuántico. que sirvió para ajustar la estructura de la banda del material y las propiedades de transporte. Aunque él y su grupo solo usaron arseniuro de indio como su semiconductor compuesto, la tecnología también debería adaptarse fácilmente a otros semiconductores compuestos III / V.

"Se necesitan investigaciones futuras sobre la escalabilidad de nuestro proceso para el procesamiento de obleas de 8 y 12 pulgadas, "Dijo Javey.

"En el futuro, creemos que los sustratos XOI se pueden obtener mediante un proceso de unión de obleas, pero nuestra técnica debería permitir fabricar transistores de tipo p y n en el mismo chip para electrónica complementaria basada en semiconductores III – V óptimos.

"Es más, este concepto se puede utilizar para integrar directamente fotodiodos de alto rendimiento, láseres y diodos emisores de luz sobre sustratos de silicio convencionales. Singularmente, esta técnica podría permitirnos estudiar las propiedades básicas de los materiales de los semiconductores inorgánicos cuando el espesor se reduce a unas pocas capas atómicas ".