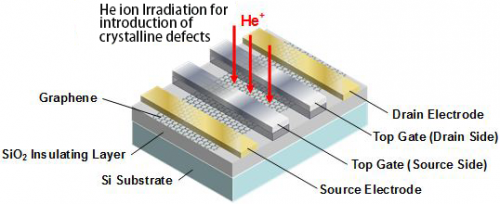

Ilustración esquemática de un prototipo de transistor de grafeno.

Los investigadores de AIST han desarrollado un transistor de grafeno con un nuevo principio operativo. En el transistor desarrollado, se colocan dos electrodos y dos puertas superiores sobre grafeno y el grafeno entre las puertas superiores se irradia con un haz de iones de helio para introducir defectos cristalinos. Los sesgos de puerta se aplican a las dos puertas superiores de forma independiente, permitiendo controlar eficazmente las densidades de portadores en las regiones de grafeno con compuerta superior. Se demostró una relación de encendido / apagado de corriente eléctrica de aproximadamente cuatro órdenes de magnitud a 200 K (aproximadamente -73 ° C). Además, su polaridad de transistor se puede controlar e invertir eléctricamente, que hasta la fecha no ha sido posible para transistores. Esta tecnología se puede utilizar en la tecnología de producción convencional de circuitos integrados basados en silicio, y se espera que contribuya a la realización de productos electrónicos de consumo de energía ultrabajo al reducir el voltaje de operación en el futuro.

Los detalles de esta tecnología se presentaron en la Reunión Internacional de Dispositivos Electrónicos de 2012 (IEDM 2012) celebrada en San Francisco, ESTADOS UNIDOS., del 10 al 12 de diciembre, 2012.

En años recientes, el aumento en el consumo de energía asociado con la expansión de terminales de información móviles y el progreso en los dispositivos de TI se ha convertido en una preocupación. Está aumentando la demanda social de reducción de la energía consumida por los dispositivos electrónicos de información. Aunque se han avanzado los intentos de reducir la energía consumida por los circuitos integrados a gran escala (LSI), se considera que la estructura de transistor convencional tiene límites inherentes. Mientras tanto, movilidad electrónica del grafeno, que representa la facilidad del movimiento de los electrones, es al menos 100 veces más grande que la del silicio. También se espera que el grafeno se pueda utilizar para resolver los problemas de los límites inherentes del silicio y otros materiales. Por lo tanto, el grafeno tiene el potencial de eliminar el obstáculo para reducir la energía consumida por los LSI, y se espera que el grafeno se utilice como material para transistores de ultra bajo consumo de energía de la era post-silicio que utilizan nuevas películas atómicas funcionales.

Figura 1:Principios de funcionamiento del nuevo transistor de grafeno y transistores convencionales.

Sin embargo, cuando se usa grafeno en un transistor de conmutación, la corriente eléctrica no puede interrumpirse lo suficiente, porque el grafeno no tiene banda prohibida. También, aunque existe tecnología para formar band gap, la movilidad de los electrones disminuye cuando se forma la banda prohibida necesaria para la conmutación. Por lo tanto, Se requiere un transistor de grafeno con un nuevo principio operativo que pueda realizar la operación de conmutación de manera efectiva con una pequeña banda prohibida.

El principio de funcionamiento del transistor de grafeno recientemente desarrollado se muestra en las Figuras 1 (a) a 1 (c). Para crear una brecha de transporte en el grafeno del canal entre las dos puertas superiores, Se utilizó un microscopio de iones de helio para irradiar iones de helio a una densidad de 6,9 x 10. 15 iones / cm 2 para introducir defectos cristalinos. La banda de energía del grafeno en ambos lados del canal se puede modular mediante control electrostático aplicando sesgos a las puertas superiores. La polaridad de los portadores en el grafeno se puede cambiar entre tipo ny tipo p, dependiendo de la polaridad de los sesgos aplicados a las puertas superiores. Cuando las polaridades en ambos lados del canal difieren, el transistor está en un estado apagado (Fig. 1 (b)). Cuando las polaridades son las mismas, el transistor está encendido (Fig. 1 (c)). Cuando un transistor convencional (Figs.1 (d) a 1 (f)) está en un estado apagado, el transporte del portador está bloqueado por una barrera formada en el extremo del lado de la fuente o del drenaje del canal que tiene el espacio de transporte. Sin embargo, como se muestra en la Fig.1 (e), la corriente de fuga del transistor en el estado apagado es grande, porque solo se forma una pequeña barrera. Mientras tanto, como muestra la figura 1 (b), la brecha de transporte en el transistor desarrollado funciona como una barrera más grande que la de los transistores convencionales (Fig. 1 (e)) y bloquea la transferencia de carga. Como resultado, es posible obtener un estado de apagado superior al de los transistores convencionales.

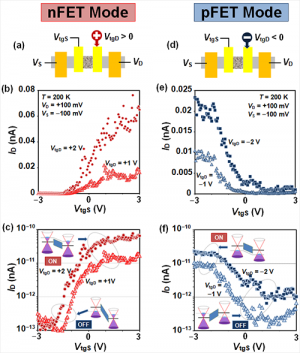

Figura 3:Relación de encendido / apagado de la corriente eléctrica del nuevo transistor de grafeno.

En el transistor desarrollado, la longitud del canal, en el que la movilidad suele deteriorarse, se puede reducir a la longitud más corta que la de los transistores convencionales. Además, debido a que el transistor desarrollado puede lograr un estado apagado eficiente con una pequeña brecha de transporte, el espacio de transporte puede hacerse más pequeño que el de los dispositivos convencionales. Debido a estas propiedades, la operación de encendido / apagado del transistor se puede realizar más rápidamente que con los transistores convencionales, y, por tanto, se cree que se puede realizar un LSI con menor consumo de energía reduciendo la tensión de funcionamiento del circuito. Además, los transistores se pueden producir utilizando la tecnología de fabricación convencional para circuitos integrados de silicio, como la litografía, declaración, y procesos de dopaje, y también se puede producir fácilmente en escala de obleas.

Para demostrar el funcionamiento del transistor del nuevo principio de funcionamiento, se fabricó un transistor formando electrodos de fuente y drenaje y un par de puertas superiores en un grafeno de una sola capa aislado del grafito. Se aplicó una dosis apropiada de iones de helio entre las puertas superiores para crear un canal irradiado con iones de helio (Fig.2, línea punteada azul), y el grafeno externo innecesario se irradió con una gran dosis de iones de helio para convertirlo en un aislante (Fig.2, línea punteada roja). Como resultado, el canal del transistor tiene 20 nm de largo y 30 nm de ancho.

Figura 4:Demostración del funcionamiento del transistor en el que la polaridad del transistor se invirtió eléctricamente. VtgD es el voltaje de puerta del lado de drenaje.

La operación de encendido / apagado del transistor fabricado se realizó a una temperatura baja de 200 K (aproximadamente -73 ° C). Los terminales de fuente y drenaje se aplicaron con polarizaciones de −100 mV y +100 mV, respectivamente. The gate bias of the drain-side gate was fixed at −2 V, and that of the source-side gate was swept from −4 V to +4 V and the electric current flowing between the source and drain electrodes was measured. An on/off ratio of approximately four orders of magnitude was observed (Fig. 3).

In the developed transistor, the on state or off state is controlled according to whether the polarities of the voltages applied to the two top gates are the same or different. Por lo tanto, by fixing one gate bias and changing its polarity, it is possible to control whether the transistor operation by sweeping the other gate voltage is n-type or p-type. In the present experiment, voltages of −100 mV and +100 mV were applied to the source and drain terminals, respectivamente. The relation between the source-drain current and the bias of the source-side gate when the gate voltage of the drain-side, V tgD , is fixed to be positive (Fig. 4(a)), is shown in Fig. 4(b). A logarithmic plot of the same data is shown in Fig. 4 (c). Aquí, when the gate voltage of the source-side is negative, the transistor is off, and when it is positive, the transistor is on. So it operates as an n-type transistor. Mientras tanto, the relation between the source-drain current and the bias of the source-side gate when the gate voltage of the drain-side is negative (Fig. 4(d)), is shown in Figs 4(e) and 4(f). En este caso, when the gate voltage of the source-side is negative, the transistor is on, and when positive, the transistor is off. So it operates as a p-type transistor. En otras palabras, it was actually demonstrated that the polarity of a single transistor can be inverted by electrostatic control.

The transistor polarity of conventional silicon transistors is determined by the type of ion for doping, so it is not possible to change the polarity once a circuit is formed. Sin embargo, because the polarity of the developed transistor can be electrostatically controlled, it is possible to realize an integrated circuit whose circuit structure can be electrically changed.

The researchers are aiming to realize CMOS operation in which transistor polarities can be changed through electrical control. They are also aiming to create a device prototype using a large-scale wafer with graphene synthesized by the CVD method (chemical vapor-phase deposition method). Al mismo tiempo, efforts to achieve higher-quality graphene will be made in order to improve the on/off ratio of electric current at room temperature and carrier mobility.