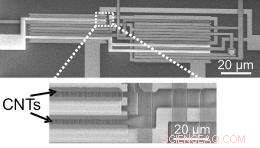

Una imagen de microscopio electrónico que muestra transistores de nanotubos de carbono (CNT) dispuestos en un circuito lógico integrado.

(PhysOrg.com) - Los ingenieros de Stanford han construido lo que creen que es un chip con los elementos de almacenamiento y computación más avanzados hechos de nanotubos de carbono hasta la fecha al idear una forma de erradicar la obstinada complicación de los nanotubos que causan cortocircuitos.

Nanotubos, que se asemejan a pajitas microscópicas de alambre de gallinero enrollado, son ampliamente vistos como la próxima generación potencial de materiales para permitir una mayor velocidad y eficiencia energética de los chips de computadora.

Los investigadores presentaron sus resultados hoy en la Reunión Internacional de Dispositivos Electrónicos (IEDM) en Baltimore, junto con otro avance en el uso de nanotubos para hacer multicapa, circuitos tridimensionales.

"Este cuerpo de trabajo ilustra que la tecnología de transistores de nanotubos de carbono se ha movido más allá del ámbito de los descubrimientos científicos y hacia la investigación en ingeniería, "dijo H.-S. Philip Wong, profesor de ingeniería eléctrica en Stanford y coautor del artículo. "Ahora podemos construir dispositivos y circuitos en una escala de obleas en lugar de demostraciones anteriores de tipo 'único en su tipo'. Los dispositivos están en un entorno de circuito que es relevante para las necesidades del sistema de hoy y del mañana".

El puñado de transistores de nanotubos en los circuitos que fabricó el equipo no se puede comparar con los cientos de millones de transistores en un microprocesador comercial o chip de memoria. pero su arreglo, la forma en que fueron hechos y sus propiedades están mucho más cerca del grado comercial que cualquier dispositivo de nanotubos fabricado antes, dijo Subhasish Mitra, profesor asistente de ciencias de la computación e ingeniería eléctrica en Stanford.

Los transistores están agrupados en las mismas secuencias "en cascada" necesarias para producir memoria y lógica computacional, y el proceso utilizado para fabricarlos es compatible con el estándar de fabricación industrial VLSI (integración a gran escala).

"Estamos muy satisfechos con el rápido progreso realizado por los profesores Wong y Mitra y sus equipos de investigación en el desarrollo de estas tecnologías para ayudar a superar las barreras para una mayor integración de circuitos electrónicos complejos basados en carbono," lo que conducirá a productos más útiles para las generaciones futuras, "dijo Betsy Weitzman, vicepresidente ejecutivo y director del Programa de Investigación del Centro de Enfoque de Semiconductor Research Corporation, que ayudó a financiar la investigación, junto con la National Science Foundation.

Los chips emplean tres técnicas avanzadas inventadas en Stanford para superar los problemas endémicos asociados con los nanotubos. Uno, inventado en 2007, permite que los transistores funcionen independientemente de que los nanotubos que los componen estén perfectamente rectos. Otro, inventado en 2008, permite la fabricación a escala VLSI de transistores de nanotubos en un chip. El anunciado hoy en el IEDM, es un proceso para eliminar de manera confiable los nanotubos que siempre conducen corriente eléctrica incluso cuando no se supone que lo hagan. Estos molestos nanotubos "metálicos" pueden provocar un cortocircuito en los transistores si no se quitan. La dificultad a la que se han enfrentado los investigadores es encontrar formas de eliminar todos los molestos nanotubos, sin dañar ninguna otra parte de un circuito, incluidos los nanotubos que se comportan correctamente.

La nueva técnica, que los investigadores llaman eliminación de nanotubos metálicos (VMR) compatible con VLSI, se basa en una idea propuesta por primera vez por Paul Collins y sus colegas de IBM en 2001. Esa idea era romper los nanotubos exponiéndolos a altas corrientes. El equipo de Stanford ha hecho ahora práctica la idea en una escala VLSI mediante la creación de una red de electrodos que eliminan los nanotubos no deseados. Esa misma rejilla de electrodos se puede grabar para producir cualquier diseño de circuito, incluidos los que hacen uso de las técnicas desarrolladas por Stanford mencionadas anteriormente.

El autor principal del artículo VMR presentado en IEDM es el estudiante graduado de ingeniería eléctrica de Stanford, Nishant Patil. Otros autores incluyen a los estudiantes graduados de ingeniería eléctrica Albert Lin, Jie Zhang y Hai Wei, y el estudiante de pregrado Kyle Anderson.

Circuitos de nanotubos tridimensionales

Cinco miembros del equipo (Wei, Patil, Lin, Wong y Mitra) siguieron inmediatamente al artículo VMR en el IEDM con otra presentación que describe el primer circuito integrado tridimensional de nanotubos de carbono multicapa.

Como estacionamientos de varios niveles, Los circuitos tridimensionales permiten empaquetar más unidades, en este caso, transistores - en un área confinada. En chips, la tercera dimensión también puede reducir la longitud de algunos cables de interconexión, reduciendo la energía requerida para la transmisión de datos. Si bien los ingenieros han comenzado recientemente a hacer progresos en la construcción de circuitos tridimensionales apilando y conectando capas hechas con materiales convencionales, el trabajo de Stanford muestra que se puede hacer con nanotubos de una manera que se integra desde el principio como un diseño 3-D, produciendo una mayor densidad de conexiones entre capas.

Indicando que el progreso puede ser posible con nanotubos, Los investigadores de Stanford pudieron crear un prototipo de chip de tres capas con docenas de transistores de nanotubos que estaban conectados en puertas lógicas funcionales mediante cableado de nanotubos y metal. ¿Qué hizo posible la hazaña? Mitra dijo:fue el uso de un proceso de temperatura relativamente baja que los investigadores desarrollaron el año pasado en el que los nanotubos se transfieren de una oblea de cuarzo a un chip de silicio.

Un desafío restante es aumentar la cantidad de nanotubos que se pueden modelar correctamente en un área determinada de un chip, para permitir la fabricación de los millones de transistores que requieren los diseños modernos. Ese no es un obstáculo que los investigadores esperan dejar sin resolver.

Ambos proyectos fueron apoyados por el Programa de Investigación del Centro de Enfoque y la Dirección de Ingeniería y Ciencias de la Información y la Computación (CISE) de la Fundación Nacional de Ciencias.

"NSF y en particular CISE, está muy interesado en explorar nuevas y emocionantes vías para obtener mejoras continuas en el rendimiento del hardware más allá de los límites de la Ley de Moore, "dijo Sampath Kannan, un director de división CISE en la National Science Foundation.

"El equipo dirigido por los profesores Mitra y Wong, apoyado por varias subvenciones del CISE, es una investigación pionera a lo largo de una de estas vías. Sus nuevos resultados sobre la técnica a escala VLSI para tratar con nanotubos de carbono metálicos para el diseño de circuitos y su demostración experimental de circuitos CNT compatibles con VLSI inmunes a las imperfecciones nos acercan a hacer de los circuitos integrados que utilizan nanotubos de carbono una realidad práctica ".

Proporcionado por la Universidad de Stanford (noticias:web)