Cinco estructuras de prueba diferentes presentan pilas de nanocables con diferentes números de niveles. La estructura inferior tiene un solo nivel; la estructura superior tiene cinco. Imágenes:Judy Hoyt, Pouya Hashemi y Leonardo Gomez

(PhysOrg.com) - Las computadoras son cada vez más potentes porque los transistores de silicio son cada vez más pequeños. Pero esa miniaturización no puede continuar mucho más sin un cambio en el diseño de los transistores, que se ha mantenido más o menos igual durante 40 años.

Un posible sucesor de los transistores de silicio actuales son los nanocables de silicio, diminutos filamentos de silicio suspendidos como las cuerdas de una guitarra entre almohadillas conductoras de electricidad. Pero si bien los nanocables de silicio son ciertamente lo suficientemente pequeños como para mantener en marcha la miniaturización de los circuitos de la computadora, ha habido dudas sobre si pueden pasar suficiente corriente eléctrica para la computación de alta velocidad. En la Reunión Internacional de Dispositivos Electrónicos de 2008, Los investigadores de Microsystems Technology Laboratories del MIT demostraron nanocables de silicio con el doble de movilidad de electrones, lo que indica la facilidad con la que se puede inducir la corriente, que sus predecesores. Ahora, el mismo grupo ha demostrado que pueden construir chips en los que se apilan hasta cinco nanocables de alto rendimiento uno encima del otro. Eso permitiría a los transistores de nanocables pasar hasta cinco veces más corriente sin ocupar más área en la superficie del chip. un paso crucial hacia el establecimiento de la viabilidad de los transistores de nanocables de silicio.

Un transistor es básicamente un interruptor:cuando está encendido, pasa una corriente eléctrica, y cuando está apagado no es así. Activar el interruptor requiere cargar una parte del transistor llamada "puerta". En el diseño actual, la puerta se encuentra en la parte superior del transistor. Pero si el transistor se vuelve lo suficientemente pequeño, la electricidad se filtrará a través de él, ya sea que la puerta esté cargada o no. Apagar el interruptor se vuelve imposible.

Debido a que los nanocables de silicio están suspendidos en el aire, la puerta se puede envolver por completo alrededor de ellos, como aislamiento alrededor de un cable eléctrico, que mejora el control del interruptor. Pero la estrechez de los nanocables limita la cantidad de corriente que pueden pasar.

La profesora de ingeniería eléctrica Judy Hoyt y sus estudiantes de posgrado Pouya Hashemi y Leonardo Gomez mejoraron el rendimiento de los transistores de nanocables de silicio al:básicamente, separar los átomos del silicio un poco más de lo que estarían naturalmente, lo que permite que los electrones fluyan a través de los cables con mayor libertad. Este "silicio tensado" ha sido una forma estándar de mejorar el rendimiento de los transistores convencionales desde 2003. Pero Hoyt fue uno de los primeros investigadores en el campo.

"A principios de la década de 1990, realmente ha desempeñado un papel pionero en la tecnología de silicio forzado, "Dice Tahir Ghani, director de tecnología e integración de transistores para el Grupo de Fabricación y Tecnología de Intel. "Hizo gran parte de este trabajo pionero que por primera vez demostró que se pueden obtener ganancias de rendimiento significativas al implementar la tensión en la tecnología de silicio". Hoyt y el trabajo de su grupo sobre nanocables de silicio tensado, Ghani dice:“Combina los dos elementos clave de los transistores”, el rendimiento y la eficiencia del espacio, “ambos son fundamentales para escalar en el futuro. Y desde ese punto de vista, lo hace muy relevante para la industria ".

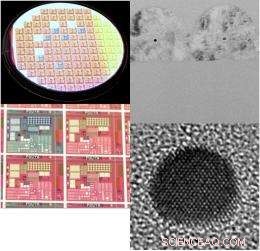

Cuatro aumentos sucesivos de un chip de prueba con circuitos de nanocables. (1) Una oblea con decenas de chips grabados. (2) Un primer plano de cuatro fichas. (3) Secciones transversales de dos nanocables en un transistor:en los centros están los nanocables; que los rodean están los elementos del transistor llamados "puertas". (4) Un primer plano del cable Imágenes:Judy Hoyt, Pouya Hashemi y Leonardo Gomez

Manejo del estrés

Para construir sus transistores de nanocables apilados, los investigadores del MIT comienzan con una oblea de silicio normal, sobre el que depositan un compuesto de silicio-germanio. Debido a que los átomos de germanio son más grandes que los átomos de silicio, las distancias entre los átomos en la capa de silicio-germanio son mayores de lo que serían en una capa de silicio puro. Cuando los investigadores depositan otra capa de silicio sobre el compuesto, los átomos de silicio intentan alinearse con los átomos debajo de ellos, entonces ellos, también, terminan espaciados ligeramente más separados.

Esta capa de silicio tenso está unida a una segunda oblea de silicio, y las otras capas se eliminan, dejando la segunda oblea cubierta con una capa base de silicio colado. Luego, los investigadores apilan capas alternas de silicio-germanio y silicio en la parte superior de la capa base, pasando su tensión a cada capa sucesiva de silicio. Usando una técnica llamada litografía por haz de electrones, los investigadores trazan líneas finas en las pilas y luego graban el material entre las líneas. Finalmente, eliminan el silicio-germanio restante, y se quedan con varias capas de nanocables de silicio suspendidos. Hoyt y sus estudiantes han fabricado nanocables con un diámetro de solo ocho nanómetros, que describieron en un artículo de 2009 en la revista Electron Device Letters del Instituto de Ingenieros Eléctricos y Electrónicos; por el contrario, los elementos más pequeños de los chips de computadora actuales tienen 45 nanómetros de diámetro.

Hoyt dice que su grupo puede crear silicio con el doble de tensión que se observa en los chips fabricados por los proveedores comerciales. "Aumentamos la fracción de germanio de la capa inicial, por lo tanto, construimos más estrés en el silicio, —Dice Hoyt. Es más, dice Hashemi, "Somos el único grupo en el mundo que ha demostrado que podemos mantener esta tensión después de la suspensión", es decir, una vez que se hayan cortado las capas subyacentes.

Hasta aquí, El grupo de Hoyt ha construido transistores de nanocables en los que la carga se transporta mediante electrones en movimiento. Pero para maximizar la eficiencia computacional, de hecho, un chip de computadora estándar usa dos tipos de transistores. En el otro tipo, la carga se lleva a cabo por los llamados agujeros. Un agujero es simplemente la ausencia de un electrón en un cristal de material semiconductor. Cuando un electrón se desliza para llenar el agujero, deja su propio lugar en el cristal; otro electrón se desliza para llenar ese lugar; etcétera. De este modo, el agujero en efecto se mueve a lo largo del cristal.

El aumento de la movilidad de los orificios en tales transistores requiere un tipo diferente de tensión:los átomos del cristal en realidad tienen que estar atascados más juntos de lo que es cómodo. Así que el grupo de Hoyt está trabajando ahora para construir nanocables a partir de un compuesto de silicio-germanio, donde las capas intermedias de silicio puro causan compresión en lugar de tensión.